# PRINCIPLED APPROACHES FOR MITIGATING MICRO-ARCHITECTURAL SIDE-CHANNEL ATTACKS

# BY

# JIYONG YU

# DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois Urbana-Champaign, 2023

# Urbana, Illinois

# Doctoral Committee:

Assistant Professor Christopher W. Fletcher, Chair

Professor Josep Torrellas

Professor Darko Marinov

Professor Trent Jaeger, Pennsylvania State University

Associate Professor Adam Morrison, Tel Aviv University

Dr. Fangfei Liu, Intel Labs

#### ABSTRACT

Micro-architectural side-channel attacks are a critical security threat that arises as a result of modern processors' pursuit of performance and efficiency. In those attacks, malicious actors exploit the micro-architectural implementation of processors to attack victim software, by monitoring how data-dependent micro-architectural resource usage varies in response to the victim's secret information. By focusing on hardware, this intricate security attack can exfiltrate sensitive information in a software-invisible manner. As future processors continue to increase in complexity, the risk posed by micro-architectural side-channel attacks is expected to escalate.

This thesis represents a significant advancement in developing secure, comprehensive, and high-performance micro-architectural side-channel mitigation solutions. While various mitigations have been proposed to address these attacks, existing approaches either target specific attack types, leaving vulnerabilities against other or future side-channel attacks open, or induce substantial performance degradation. The ideal mitigation solution, therefore, should both offer strong and comprehensive security guarantees while maintaining modest performance overhead.

To overcome these challenges, the key idea underpinning our solutions is enforcing information-flow properties at the hardware level: once all side-channel vulnerabilities are identified, and all secret information is correctly tracked and annotated, blocking micro-architectural side-channel leakage is simply preventing side channels from consuming the secret. Based on this key idea, we developed the data-oblivious ISA (OISA), which for the first time, incorporates side-channel-specific security specification at the ISA level and enforces the desired information-flow properties in commodity hardware. To address the recent surge of speculative side-channel attacks, we further designed Speculative Taint Tracking (STT), which employs the same principle for achieving provable security against speculative side channels in general. We further improve the performance of STT with Speculative Data-Oblivious Execution (SDO) without sacrificing its security properties.

In addition to the proposed mitigation frameworks, we also examined several existing point-mitigation strategies and developed new attacks circumventing those mitigations. We demonstrated how common control-flow leakage attack mitigations fail with a new attack variant capable of extracting the byte-granular PC information of arbitrary victim's dynamic instruction. We also showcased why eliminating timers is insufficient in blocking cache side-channel attacks by identifying new primitives for monitoring cache state. Although

these attacks may be further mitigated with new point defenses, our claim is that defending against micro-architectural side-channel attacks should not become a cat-and-mouse game. Instead, comprehensive mitigations, such as the solutions proposed in this thesis, should be adopted to effectively combat current and future attacks.

To My Families.

#### ACKNOWLEDGMENTS

Completing a Ph.D. in computer science from one of the top schools in the world is a challenging and demanding journey, filled with uncertainties and immense pressure. However, it is also a path that brings moments of joy, encouragement, and personal growth. There is no way I can be where I am today without the support and motivation of numerous individuals who have played pivotal roles in my life.

First and foremost, I would like to express my utmost gratitude and respect to my advisor, Chris Fletcher. He accepted me as one of his first students, when I barely knew anything about doing research, and guided me throughout this six-year Ph.D. journey. In my honest opinion, Chris is not only an exceptional advisor, but also a perfect human being ("perfect" is usually not in the dictionary of a researcher/scientist; but I feel like it's the right word for Chris). He is kind, smart, humorous, diligent, and consistently displays unwavering enthusiasm and positivity towards research. He is patient and empathetic to every student and always maintains great relationships with every one of his colleagues. I can easily write another thesis solely focusing on his outstanding qualities. The most invaluable part of my graduate school career was learning from Chris, from developing skills for conducting research projects from start to finish, to how to treat people around me with respect and kindness. I will definitely miss the days when I knocked on your door and asked whether you have time for a project update so that I can soak up more knowledge and wisdom during our meetings. I wish you all the best in your future career as a tenured professor.

Second, I would extend my gratitude to some of my close collaborators, who also graciously served as members of my Ph.D. thesis committee: Josep Torrellas, Darko Marinov, Adam Morrison, Trent Jaeger, and Fangfei Liu. An important piece of my Ph.D. career is the regular project meetings we had, where we would discuss progress and problems. It was during these meetings that I gained a wealth of knowledge from each and every one of you. Josep, Darko, and Trent, all being distinguished and highly respected senior professors in computer architecture and system security fields, taught me valuable lessons on becoming a true researcher with their remarkable abilities to identify those problems and communicate complex concepts. Adam and Fangfei, with their sharp intellects, consistently raised thought-provoking questions that pinpointed critical aspects we might have overlooked. To me, you all are truly the best professors and researchers in this field, and it has been my greatest privilege to work with all of you.

Next, I would express my appreciation to my incredible lab mates: Kartik Hedge, Hadi

Asgharimoghaddam, Jose Rodrigo Sanchez Vicarte, Rohit Agrawal, Mohamad El-Hajj, Riccardo Paccagnella, Sushant Dinesh, Rutvik Choudhary, Nandeeka Nayak, Hannah Liang, and Boru Chen. It is a great experience working alongside all of you in one lab, engaging in discussions about research ideas during the weekly meetings, and chatting about everything during our leisure time. When I look back, the most memorable part about Ph.D. was working late nights with you guys in the lab fighting for the paper deadlines—it's certainly not fun and usually filled with distress and pain, but only through these hardships can we become better. There is an old Chinese saying by Confucius that states: "When three people walk together, there must be one who can be my teacher". However, I must say that all of you have been my teacher. Working with all of you and developing close friendships with you guys has been an invaluable asset throughout my years in graduate school. To those of you who have graduated, I wish you all the best in your post-Ph.D. career. And to those of you who are still students, I wish you a successful and fruitful Ph.D. journey.

Next, I have been fortunate to work with several industry researchers during my internships at Intel Labs and Microsoft Research. These experiences provided me with profound insight to propel my own research studies. I would like to thank Carlos Rozas, Frank Mckeen, Fangfei Liu (once again), Thomas Unterluggauer, Ron Gabor at Intel, and Weidong Cui, Xinyang Ge at Microsoft Research for sharing your profound knowledge and providing me guidance during my summer internships. I hope one day in the future I would have to opportunity to work with you again.

I would also like to thank many other people who helped me during my years at UIUC. First, I want to thank Mengjia Yan for her guidance in my early years; her work has shown me why hardware security is a great field for research. Second, I want to thank my advisor and mentors in my undergraduate years at the University of Michigan. I am so grateful to Prof. Trevor Mudge and Prof. Jason Mars who opened up the gate of computer architecture research for me. Third, I would like to thank my friends, including but not limited to: Jinyang Li, Zirui Zhao, Houxiang Ji, Jing Ying, Liming Yang, Ruijie Wang, Tianshi Wang, Yunan Zhang, Dongxing Liu, Yihan Pang, Boyuan Tian, Yifan Yuan, Jingcheng Ma. "True friends are like stars, you may not always see them, but you know they are always there." Although I would not be in Champaign anymore with you all, I firmly believe that distance will not diminish our friendship, and I look forward to reuniting with you all in the future.

Last but definitely not least, the true heroes are all my family members, including my dear wife Ru Huang. I have not seen my parents and grandparents for more than three years until this moment. However, every time I see them through video chat I can feel the love and support they have for me. For instance, my grandma always ensures that I am healthy and not getting covid, and my father patiently acts as an amplifier, trying to repeat every

word I said (my grandma's hearing is impaired). Words cannot describe how much I miss you and I will be back to see you all as soon as I can. My wife, Ru Huang, is a true blessing in my life. Since we met each other during the start of the pandemic, he has been by my side, giving me all the love and support I can ask for, and also encouraging me to pursue what I want. I promise that I will not let any of you down and will continue to strive for excellence throughout my career.

# TABLE OF CONTENTS

| CHAPT  | FER 1 INTRODUCTION                                                  |

|--------|---------------------------------------------------------------------|

| 1.1    | Micro-Architectural Side-Channel Attacks                            |

| 1.2    | Problems of Existing Micro-Architectural Side-Channel Mitigations 2 |

| 1.3    | Thesis Contributions and Organization                               |

|        |                                                                     |

| CHAPT  |                                                                     |

| 2.1    | Processor Optimizations                                             |

| 2.2    | Overview of Micro-Architectural Side-Channel Attack                 |

| 2.3    | Classic Side-Channel Attacks                                        |

| 2.4    | Speculative Side-Channel Attacks                                    |

| 2.5    | Mitigations for Classic Side-Channel Attacks                        |

| 2.6    | Mitigations for Speculative Side-Channel Attacks                    |

| O 1    |                                                                     |

|        | TER 3 DATA-OBLIVIOUS ISA                                            |

| 3.1    | Introduction                                                        |

| 3.2    | Threat Model                                                        |

| 3.3    | Data-Oblivious Execution                                            |

| 3.4    | Data-Oblivious ISAs                                                 |

| 3.5    | Implementation                                                      |

| 3.6    | Security Analysis                                                   |

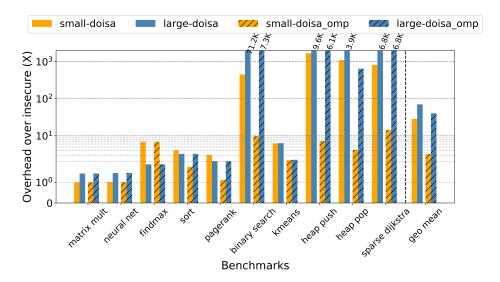

| 3.7    | Evaluation                                                          |

| 3.8    | Other Related Work                                                  |

| 3.9    | Conclusion                                                          |

| CILADE | PED 4 ODECHI ATIVE TA INT TO A CIVING                               |

| CHAPT  |                                                                     |

| 4.1    | Introduction                                                        |

| 4.2    | Threat Model                                                        |

| 4.3    | Covert Channels in Speculative Execution Attacks                    |

| 4.4    | Speculative Taint Tracking                                          |

| 4.5    | Microarchitecture                                                   |

| 4.6    | Security Analysis                                                   |

| 4.7    | Evaluation                                                          |

| 4.8    | Conclusion                                                          |

| CHAPT  | ΓER 5 SPECULATIVE DATA-OBLIVIOUS EXECUTION 95                       |

| 5.1    | Introduction                                                        |

| 5.2    | Motivation: Improving Speculative Taint Tracking                    |

| 5.3    | Speculative Data-Oblivious Execution                                |

| ().()  | - >>>>+++++++++++++++++++++++++++++++++                             |

| 5.4                          | Speculative Data-Oblivious Loads         | 101 |

|------------------------------|------------------------------------------|-----|

| 5.5                          | Microarchitecture                        | 109 |

| 5.6                          | Security                                 | 113 |

| 5.7                          | Evaluation                               | 115 |

| 5.8                          | Conclusion                               | 119 |

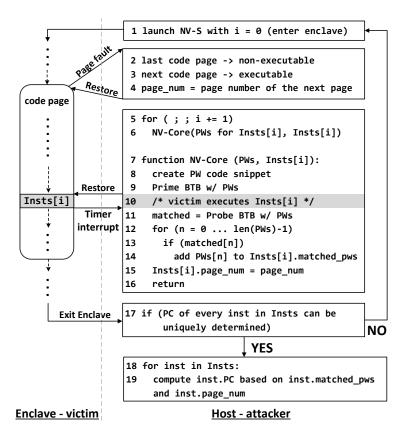

| CHAPTER 6 NIGHTVISION ATTACK |                                          |     |

| 6.1                          | Introduction                             | 120 |

| 6.2                          | BTB Mechanism                            | 123 |

| 6.3                          | Attack Models and NightVision Overview   | 129 |

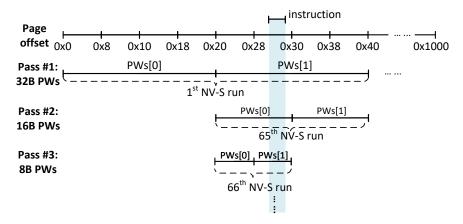

| 6.4                          | NIGHTVISION Attack Design                | 130 |

| 6.5                          | Use Case 1: Control-Flow Leakage Attacks | 134 |

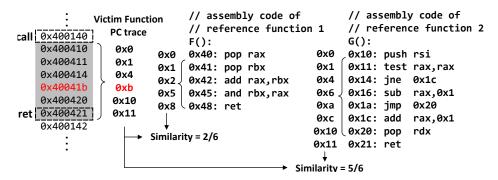

| 6.6                          | Use Case 2: Fingerprinting Private Code  | 136 |

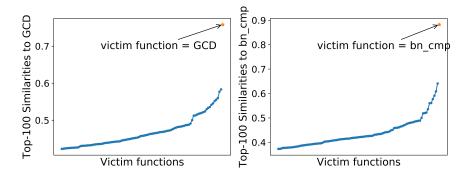

| 6.7                          | Evaluation                               | 141 |

| 6.8                          | Discussion                               | 145 |

| 6.9                          | Other Related Work                       | 147 |

| 6.10                         | Conclusion                               | 148 |

| CHAPT                        | TER 7 SYNCHRONIZATION STORAGE CHANNELS   | 149 |

| 7.1                          | Introduction                             | 149 |

| 7.2                          | Cache Side-Channel Attacks               | 152 |

| 7.3                          | Apple M1                                 | 153 |

| 7.4                          | New Attack Primitive on M1 using LL/SC   | 155 |

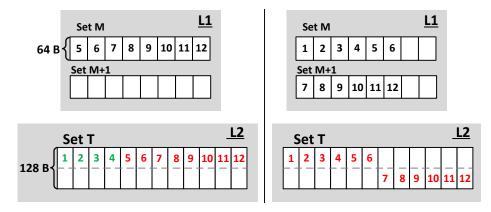

| 7.5                          | Reverse-Engineering M1's Shared L2 Cache | 158 |

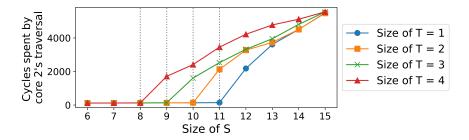

| 7.6                          | Monitoring a Single Cache Set            | 165 |

| 7.7                          |                                          | 169 |

| 7.8                          | Evaluation                               | 171 |

| 7.9                          | Discussion                               | 175 |

| 7.10                         | Conclusion                               | 177 |

| СНАРТ                        | TER 8 CONCLUSIONS                        | 178 |

| REFER                        | ENCES                                    | 180 |

#### CHAPTER 1: INTRODUCTION

Over the past several decades, the third industrial revolution—also referred to as the digital revolution—has brought sweeping changes to every corner of the world, influencing every aspect of human life, including education, communication, work, and entertainment. Central to this revolution lies the development of microprocessors, which have unleashed immense computing power and catalyzed innovations across various disciplines. And critical to the advancement of microprocessors is computer architecture design, which has continuously pushed the boundaries of computer performance and efficiency with innovations in underlying hardware structures and organizations.

However, in the late 1990s, researchers began to realize that the growing sophistication of those processor design optimizations may lead to serious security issues, known as micro-architectural side channels, leaking sensitive data stealthily across mutually distrusted parties [1]. Since then, many processor structures and optimizations have been exploited as side-channel attacks, ranging from the initial cache attack [2], to more recent speculative execution attacks [3, 4]. Those attacks have proven to cause a wide range of security and privacy threats, from breaking cryptographic implementations [5, 6, 7], stealing personal information [8, 9], to monitoring user activities [10, 11, 12], and in the worst case scenario, leaking the entirety of the program memory [4]. With modern processors persisting in seeking performance and efficiency by incorporating more sophisticated, but potentially more vulnerable designs, mitigating micro-architectural side-channel attacks has become a matter of utmost urgency.

#### 1.1 MICRO-ARCHITECTURAL SIDE-CHANNEL ATTACKS

Computation is a process of generating output from a given input based on a protocol that defines the input-output relationship. The protocol can take various forms depending on the level of abstraction. At the software level, a protocol can be a program written to process some user input; while at the hardware level, a protocol can be a combinational circuit describing the transitions of the register state. Cyber-attackers develop techniques to attack these protocols in different computing systems to undermine different security properties, such as confidentiality and integrity.

Side-channel attacks are a common type of attack that targets confidentiality. The fundamental difference between side-channel attacks and other common attacks, such as memory corruption attacks [13], lies in how they exploit the protocol. Common attacks target

the design errors within the protocol itself, such as program bugs, coercing the protocols into behaving in unintended ways, ultimately generating output directly revealing the secret input. In contrast, side-channel attacks do not rely on any program bugs to misuse the protocol. The key insight of side-channel attacks is that, protocols implemented in the real world inherently produce various forms of computational side effects that depend on the input. By measuring those computational side effects, side-channel attacks may obtain information about the secret input through the correlation between the observed side effects and the input, as illustrated in Figure 1.1a [14].

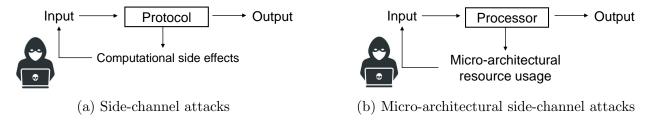

Figure 1.1: Relationship between side-channel attacks and micro-architectural side-channel attack

Micro-architectural side-channel attacks constitute a significant class of side-channel attacks. In these attacks, as shown in Figure 1.1b, the attacker focuses on the practical implementation of processors, with the objective of learning the secret input through its measurement of the micro-architectural resource usage resulting from processing the input on the targeted processor. This approach is driven by the fact that many micro-architectural structures incur data-dependent state changes: as an example, the location of data within a processor cache directly depends on the data address. Therefore, an attacker aware of the data's residency inside the cache can easily deduce information about the data address.

Since the discovery of micro-architectural side-channel attacks, numerous hardware structures have been exploited as side channels, such as cache [5, 15], Translation Lookaside Buffers (TLBs) [16], predictors [17, 18, 19, 20], micro-op caches [21], execution units [22], and data prefetchers [23, 24]. As the complexity of modern microprocessors continues to evolve, more and more side-channel vulnerabilities will likely be discovered in the future.

# 1.2 PROBLEMS OF EXISTING MICRO-ARCHITECTURAL SIDE-CHANNEL MITIGATIONS

With the emergence of micro-architectural side-channel attacks as a critical security threat, it is imperative for researchers and practitioners to develop effective strategies for mitigating those attacks. Unfortunately, existing mitigations either deliver weak and limited security guarantees, or induce substantial performance degradation.

For instance, researchers have proposed secure hardware designs to fix processor components prone to side-channel attacks, including secure cache [25], secure TLB [26], and others. However, given a processor is a synergy of numerous different hardware components, fixing vulnerabilities individually without a comprehensive study of the entire processor is bound to be incomplete.

There have also been protection schemes aimed at comprehensively mitigating microarchitectural side channels. One straightforward solution is to eliminate resource sharing by running the victim program on dedicated hardware exclusively. While this approach can be considered comprehensive as it prevents attackers from observing the hardware usage (since most micro-architectural side-channel attacks require co-residency with the victim program), it is impractical for general applications. Modern processors are designed to handle multiple tasks simultaneously [27], so restricting a processor to a single victim software would lead to significant resource under-utilization, which may further exacerbate as future processors pursue more aggressive parallel processing.

Another popular approach that claims to comprehensively mitigate micro-architectural side channels without relying on physical isolation is data-oblivious programming. Data-oblivious programming encapsulates a series of secure coding practices with the goal of eliminating any secret-dependent hardware usage. Yet, achieving data obliviousness usually entails introducing redundant operations to conceal the actual secret-dependent execution behavior, resulting in significant performance overhead in practice.

## 1.3 THESIS CONTRIBUTIONS AND ORGANIZATION

Given the limitations of existing micro-architectural side-channel mitigations, the main objective of this thesis is to design hardware-based mitigations that deliver strong and comprehensive security guarantees that cover micro-architectural side-channel attacks broadly, and at the same time minimizing the performance overhead caused by the defense mechanism. Central to our solution is the key idea of consolidating different individual side-channel attacks into general and clear micro-architectural side-channel abstractions. These abstractions serve as micro-architectural specifications to help enforce security policies in hardware designs, and offer a unified protection mechanism for different, and even future attacks.

Our abstractions are directly inspired by the existing information flow literature [28]. At a high level, our abstractions define *secrets* as data inside micro-architecture that requires protection. In addition, data-dependent hardware execution behaviors are classified as *channels*. Thus, mitigating micro-architectural side-channel attacks can be formulated as blocking the information flow from any secrets to the identified channels. The benefit of this

methodology is two-fold. In terms of security, preventing the channels from ever consuming secrets comprehensively blocks different types of side-channel leakages. Performance-wise, the protection mechanism is relaxed whenever possible, for example when processing public data (non-secrets), or when any data is processed by data-independent hardware execution (non-channels).

This thesis consists of two parts. First, this thesis presents several side-channel protection frameworks which demonstrate how specifying proper abstractions helps to mitigate side-channel attacks comprehensively and efficiently. Chapter 3 describes OISA, which applies this methodology at the hardware-software interface level, by specifying the concept of secrets and channels through new instruction-set architecture (ISA) extensions. The new side-channel-centric security definition introduced by OISA can be used to guide the development of side-channel-resistant hardware, and simultaneously enable provable side-channel-free programming. While OISA concentrates on micro-architectural side-channel attacks in general, Chapter 4 and 5 introduce new abstractions for the more recent speculative execution attacks. The two proposed mitigations, named STT and SDO, apply the security abstractions originated from OISA to construct software-invisible defenses that overcome the additional security threats introduced by speculative execution attacks with tolerable performance costs.

Second, we pinpoint the weaknesses of existing point mitigations in concrete side-channel attack scenarios, thereby advocating for the adoption of robust and comprehensive mitigations such as our proposed schemes, as such schemes have not yet been implemented in real processors. In Chapter 6, we investigate the idea of fixing side-channel vulnerabilities by introducing code transformations in response to new side-channel attacks, specifically in the context of control-flow inference attacks. Our study presents a new instance of control-flow leakage attacks that exposes new attack opportunities and surpasses state-of-the-art defenses. Chapter 7 explains in practice how constraining the attacker's observability over the microarchitectural state fails, as modern complex hardware contains hidden primitives that enable the attacker to retrieve micro-architectural state information.

We now present the organization of the thesis with the overview of each chapter.

Chapter 2 – Background This chapter presents a framework for understanding microarchitectural side-channel attacks, which can be divided into classic side-channel attacks and more recent speculative side-channel attacks. We explain how these two types of attack work and the important part of the attack process, using existing attacks as examples. We also discuss mitigations for these attacks. Chapter 3 – Data-Oblivious ISA (OISA) This chapter presents OISA—a hardware-software interface that enables formally-provable, portable, and performant side-channel-free programming. OISA is built upon data-oblivious programming, a technique that theoretically eliminates micro-architectural side-channels, but in practice remains vulnerable due to the lack of security guarantees from the hardware. OISA provides a security specification that establishes the security foundation for data-oblivious programming while maintaining the flexibility required for designing hardware optimizations.

The idea behind OISA is a combination of new ISA-level security specifications with hardware information-flow tracking. The new ISA allows programmers to directly communicate data secrecy with the hardware (rather than indirectly, e.g., via encryption [29]). OISA also directly exposes any potential micro-architectural side channels in the form of unsafe instruction operands. Therefore, eliminating side-channel leakage is equivalent to preventing the information flow from any secret data to unsafe operands—we demonstrate how to achieve this by presenting an implementation of OISA architecture on an existing processor. This methodology not only ensures security against traditional side-channel attacks but also the recent speculative side-channel attacks without any special handling.

This work appears in [30] and won the following awards:

- Distinguished Paper Award Honorable Mentions at NDSS'19

- CSAW'19 Applied Research Finalists

- IEEE MICRO Top Picks, 2020

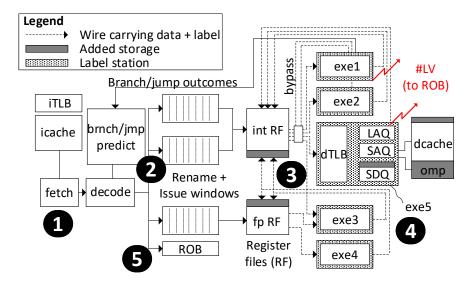

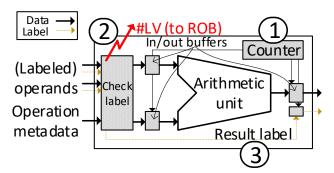

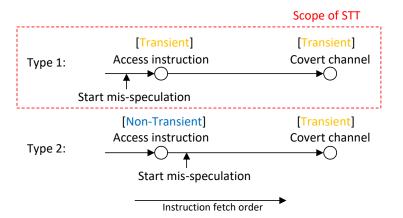

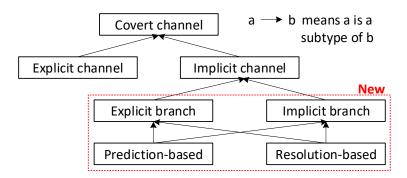

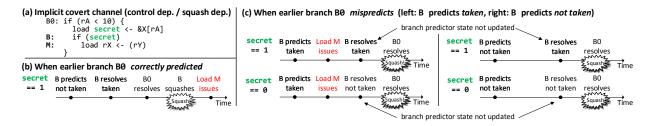

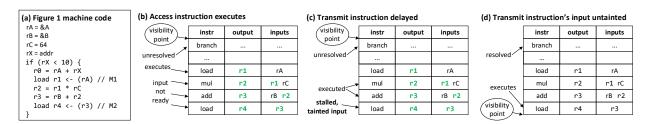

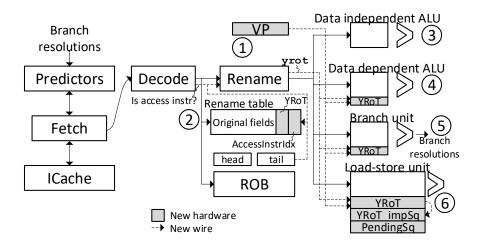

Chapter 4 – Speculative Taint Tracking (STT) This chapter presents a novel protection framework named STT, which comprehensively mitigates speculative execution attacks. STT makes two key contributions: first, it presents a comprehensive classification of hardware mechanisms (referred to as covert channels) that might transmit speculative data to the attacker's execution context, in the form of data-dependent hardware resource usage. These covert channels manifest as explicit channels and implicit channels, akin to the explicit flow and the implicit flow in the program analysis literature. Second, STT applies OISA's methodology of mitigating micro-architectural side channels to speculative execution attacks only, by leveraging hardware-level information-flow tracking that prevents secret-dependent data from being consumed by identified covert channels during the execution of transmitter instructions. This prevention is implemented in a conservative manner in STT: the speculative execution of transmitter instructions that deliver secrets to covert channels is delayed until non-speculative. But like OISA, the protection is only enforced when the leakage is possible, which effectively reduces the performance cost of the overall mitigation.

This work appears in [31] and won the following awards:

- Best Paper Award at MICRO'19

- IEEE MICRO Top Picks, 2020

- Communication of ACM Research Highlight, 2021

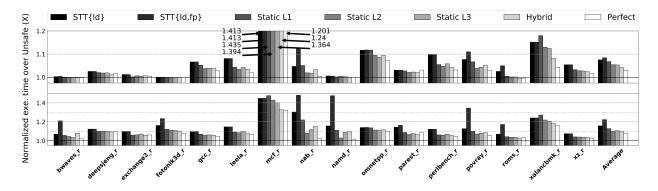

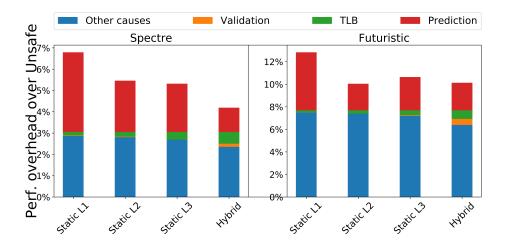

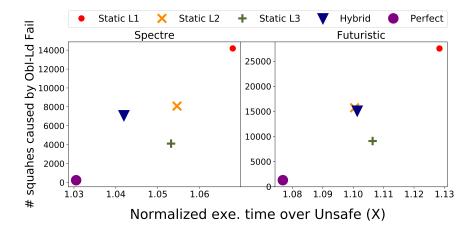

Chapter 5 – Speculative Data-Oblivious Execution (SDO) This chapter introduces SDO, a protection framework that builds on top of STT to achieve higher performance without compromising STT's strong security guarantee. Since the performance overhead of STT is mostly due to the delay of transmitter instruction's execution when it involves covert channels consuming speculative secrets, SDO devises novel mechanisms to proceed with the execution. Inspired by OISA, SDO partially achieves this goal with data-oblivious execution hardware, whose execution is independent of sensitive data.

However, despite its security, data-oblivious execution involves significant redundant work that usually offsets the benefit of executing unsafe transmitters early. Here comes the major contribution of SDO: we for the first time demonstrate how prediction/speculation can assist in mitigating speculative attacks, despite being the root cause of those attacks. In short, SDO utilizes prediction to reduce the baseline data-oblivious execution down to a smaller set of hardware activities that still maintain data obliviousness, and eventually delivers a net performance gain.

This work appears in [32] and won first place in the Inaugural Intel Hardware Security Academic Award in 2021.

Chapter 6 – NightVision Attack This chapter presents a novel micro-architectural side-channel attack called NightVision that is capable of directly observing the exact address of arbitrary victim dynamic instructions. NightVision leverages several overlooked characteristics of Branch Target Buffers in modern processors, and shows how this predictor structure, while commonly considered only relative to control instructions, can also lead to observation of the execution of non-control instructions. NightVision's capability of extracting PCs of potentially any victim dynamic instructions naturally surpasses prior control-flow leakage attacks that infer secret information through its impact on program control-flow, and overcomes corresponding software mitigations. In addition, NightVision enables new opportunities in binary fingerprinting—allowing an attacker to identify unknown victim programs through their dynamic instruction address footprints.

This work appears in [33].

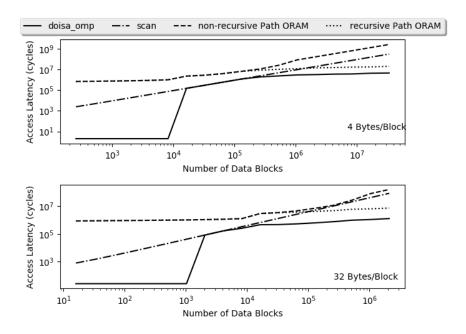

Chapter 7 – Synchronization Storage Channel (S<sup>2</sup>C) This chapter presents a novel timer-less cache side-channel attack that exploits hardware synchronization instructions, specifically load-linked/store-conditional (LL/SC) instructions. This attack, dubbed S<sup>2</sup>C, aims at eliminating the reliance on high-resolution timing measurements in existing cache attacks. S<sup>2</sup>C exposes how the implementation of LL/SC on modern Apple processors allows an attacker to directly read private cache evictions as the SC return value. With this vulnerability, S<sup>2</sup>C further develops several techniques to expand the attacker's observability toward activities within multiple shared cache sets. The end result is a cache side-channel attack with the same threat as state-of-the-art cache attacks [5, 34, 35] without depending on the existence of high-resolution timers.

This work will appear in [36].

Chapter 8 – Conclusion This chapter summarizes the thesis and addresses possible directions for future research.

#### CHAPTER 2: BACKGROUND

#### 2.1 PROCESSOR OPTIMIZATIONS

Modern processors integrate a wide range of processor optimizations to enhance performance and efficiency. Unfortunately, many of those optimizations exhibit data-dependent behavior which the attacker can exploit for mounting micro-architectural side channels. Before delving into those attacks, it is important to first highlight the most common processor optimizations, as they form the foundation for most identified side-channel attacks.

# 2.1.1 Processor Pipelining and Out-of-order Execution

Modern processors use dynamic scheduling to execute instructions in parallel and out of program order to improve performance [37, 38]. This is achieved by dividing the processing of instructions into multiple pipeline stages. Initially, instructions are fetched into the processor pipeline at the fetch stage, and issued to reservation stations for scheduling at the issue stage, all following the program order. All pipeline stages up to this point are usually referred to the processor frontend. The execution of instructions at the execution stage is out of program order. Finally, at the retire (also called commit) stage, instructions retire as they make their operation externally visible by irrevocably modifying the architectural system state in program order. The pipeline stages starting from the execution stage until the retire stage are referred to as the processor backend. The in-order retirement is implemented by queuing instructions in a reorder buffer (ROB) [39] in the instruction fetch order and dequeuing a completed instruction when it reaches the ROB head.

#### 2.1.2 Prediction and Speculation

Speculative execution improves performance by executing instructions whose validity is uncertain instead of waiting to determine their validity. If such a speculatively-executed instruction turns out to be valid, it is eventually retired; otherwise, it is *squashed* and the processor's state is rolled back to the prior state when speculation starts. As a byproduct, all the following instructions also get squashed. That is, a squash causes a large pipeline disturbance. However, if the speculation is done correctly, the processor can execute instructions that would have been delayed, leading to a significant performance improvement.

To facilitate speculative execution, modern processors employ multiple hardware prediction mechanisms for determining when and how speculation should be performed. The most common prediction mechanism is the branch predictor for predicting the direction and target of control-transfer instructions. Branch predictors in today's processors are sophisticated hardware logic structures that can be trained to learn the program's control-flow behavior, and make predictions based on the current program counter value alone. Additionally, memory dependency prediction is another prevalent prediction mechanism for predicting dependencies between memory loads and stores before their address operands are ready. Other prediction strategies such as value prediction have also been proposed for improving processor performance [40].

# 2.1.3 Superscalar processing

Super-scalar processing is a fundamental performance optimization for executing multiple instructions within a single instruction stream at any clock cycle. A superscalar processor augments its hardware resources, such as buffers, execution units, and reservation stations, allowing every pipeline stage— such as fetch, decode, issue, execute and commit—to handle multiple instructions per cycle. The maximal number of instructions that can be possibly processed by a superscalar pipeline simultaneously is usually called *pipeline width*. When combined with other optimizations such as processor pipelining and speculative execution, superscalar processors achieve a high level of instruction-level parallelism and overall computation throughput.

The instruction-level parallelism achieved by superscalar processing is inherently restricted by the interdependency between instructions, as the execution of mutually-dependent instructions has to be serialized. Programs with fewer inter-instruction dependencies thus benefit more from superscalar processing. On the other hand, superscalar machines must employ dedicated hardware logic for checking instruction dependencies, whose complexity scales super-linearly with the pipeline width. Consequently, most real-world processors typically opt for modest pipeline widths (typically around 4 to 8).

## 2.1.4 Multi-threading, Multi-core, Multi-processor

Simultaneous multi-threading, multi-core, and multi-processor are basic performance optimization aiming at improving the resource utilization by concurrently running multiple programs at different levels of processors. Simultaneous multi-threading, or SMT [41], allows each processor core to simultaneously run multiple hardware threads, such that a hardware thread can use core resource that is not currently used by other threads. While individual thread performance may be negatively impacted by resource competition with other threads,

the overall utilization of the execution units within the core pipeline is maximized, resulting in a substantial throughput improvement.

Multi-core and multi-processor achieve a lower-level of resource sharing compared to SMT. With multi-core, processor cores can share lower-level resources, such as shared caches and memory controllers. The prevalence of multi-core processors is evident in the contemporary computing landscape, with the core count in state-of-the-art processors continuously increasing to meet the demands of modern computing tasks [42]. Multi-processor architecture aims at building large, expansive interconnected computer networks by linking a large number of processors together. This allows each processor to share data with other processors through high-speed interconnects.

## 2.1.5 Caching

Caching is essential optimization to alleviate the performance impact of memory (DRAM) accesses. Since accessing main memory is a slow process that may yield a significant performance bottleneck, modern processors adopt small and fast on-chip storage units called caches for storing frequently used data. By doing so, caching benefits applications with good locality by transforming slow DRAM accesses into fast cache accesses.

Processor caches operate as lookup tables, mapping addresses to corresponding data. Based on how cache access logic locates the target data, caches can be categorized into three types: directed-mapped, fully-associative and way-associative caches, among which the way-associative cache is the most popular option for modern processors. A way-associative cache is organized into cache sets, where each set is associated with a specific subset of address bits called set index bits. Each cache set consists of N cache lines, where N represents a number of ways, and each cache line stores a fixed number of contiguous bytes. During a cache access, the cache access logic first uses cache set index bits to locate a cache set, which contains cached data that share the same set index bits. The remaining address bits are then used to identify the target data within the set. When the data is present in the cache (called a cache hit), it is retrieved and returned to the pipeline. If the data is not found (a cache miss), the next cache level (or the memory) will be accessed.

Most processors nowadays adopt a multi-level cache hierarchy. The highest-level caches are typically private to each core and have smaller sizes compared to lower-level caches, allowing for short access latency. The lower-level caches are larger in size and are commonly shared between multiple processor cores. As a trade-off, they store more frequently-used data but come with longer access latency. The specific organization of the cache hierarchy is implementation-dependent and varies across different processors.

#### 2.2 OVERVIEW OF MICRO-ARCHITECTURAL SIDE-CHANNEL ATTACK

Micro-architectural side-channel attacks are attacks exploiting the incidental computational side effects resulting from running programs on real processors, to infer secret information processed by the processor. Those side effects include but are not limited to timing [1], power [43], temperature [44], and hardware activity statistics reported by the hardware performance counters. Modern processors provide primitives for directly obtaining these side effects at the software level, making micro-architectural side-channel attacks possible with only software effort.

Micro-architectural side-channel attacks can be categorized into two large types based on the attacker's proximity to the victim program. First, there are remote attacks, where the attacker needs not co-reside with the victim software on the same computing platform. The attacker simply interacts with the victim (e.g., via a caller-callee relationship) from remote and obtains the side effect associated with the victim's computation. Timing is the most commonly exploited side effect in this case, which has inspired the remote timing attack—a common side-channel attack paradigm where the attacker can remotely invoke the vulnerable program and obtain accurate program execution timing. For instance, Paul Kocher utilized end-to-end program execution timing to learn secret data in cryptographic systems [1]. While many remote timing attacks only exploit the data-dependent behavior at the program level [45, 46, 47, 48], data-dependent micro-architectural designs also significantly influences the program timing [49, 50]. Other side effects, like power [50, 51, 52] could be exploited in a similar manner. Despite the advantage of not relying on resource sharing between the attacker and the victim, the coarse-grained, end-to-end measurement of the side effect is typically susceptible to a low signal-to-noise ratio in today's computing systems. Therefore, large numbers of repeated experiments are necessary for extracting a clear correlation between the measured side effect and the target secret value.

The second attack setting, assumed by most micro-architectural side-channel attacks, leverages the multi-tenancy in modern computing systems. Multi-tenancy is ubiquitous nowadays: browsers on personal devices can connect to websites from independent hosts; cloud computing platforms such as Amazon AWS [53] and Microsoft Azure [54] normally use the same processor for hosting services belonging to different customers for higher resource utilization. In this co-location attack setting, the attacker can interact with the hardware directly through their own programs. Consequently, instead of relying on coarse-grained, end-to-end side-channel measurements, the attacker can directly monitor the victim program's micro-architectural resource usage. By observing the appropriate hardware resource in a precise manner, the measured side effect establishes a much more accurate correlation with the

victim's secret information. Furthermore, direct interaction with the victim is not necessary for the co-location attack setting. This work presents mitigation methods applicable to both settings, with a primary emphasis on the co-location setting since this scenario presents a clear view of how different hardware resources function as side channels and enable information leakage.

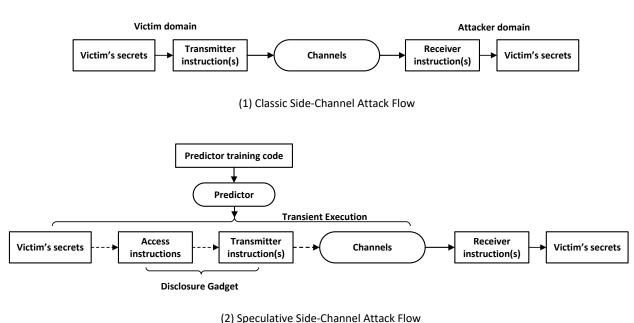

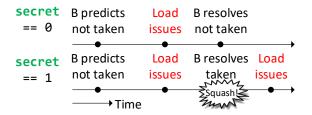

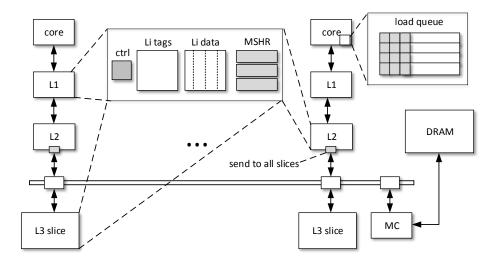

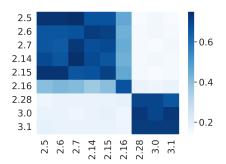

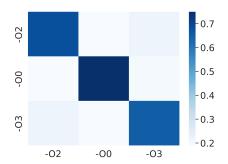

Over the years, countless micro-architectural side-channel attacks have been developed to exploit weaknesses in the design of various components in current processors for leaking sensitive information. To implement effective countermeasures, it is crucial to understand each individual attack as well as the underlying principles behind all attacks. Therefore, in this section, we further classify co-location-based attacks into two categories: classic (non-speculative) side-channel attacks and speculative side-channel attacks. We highlight the relationship between these two categories, the individual attacks they encompass, and the common mitigations employed against these attacks. Inspired by the prior work DAWG [55], we introduce abstract models for describing the classic and speculative attack procedures, as illustrated in Figure 2.1.

Figure 2.1: Classic and speculative side-channel attack procedures. Regular squares represent software components; rounded-corner squares are hardware components. Dotted arrows denote information flow via transient execution.

The rest of this chapter will describe classic (Section 2.3) and speculative attacks (Section 2.4) in detail, as well as the existing mitigations for both types of attacks (Section 2.5 and 2.6).

#### 2.3 CLASSIC SIDE-CHANNEL ATTACKS

As Figure 2.1 (1) showns, a classic micro-architectural side-channel attack requires the victim program to contain transmitter instructions (or transmitters) that operate on the victim program secrets. The key to micro-architectural side-channel attacks is that, modern processors contain various hardware resources and optimizations that act as channels, such that the execution of transmitter instructions inadvertently transmit secrets through the channel. To capture the secret-dependent resource usage happened to those channels, the attacker carefully selects receiver instructions (or receivers) and when and how to execute those instructions. The receiver instructions interact with the channel, and generate computational side effects which is precisely correlated with the transmitted information.

Importantly, the transmission of secret information is never the intended purpose of the victim<sup>1</sup>. In the following, we describe classic side-channel attacks based on these three components: channels, transmitter instructions, and receiver instructions.

#### 2.3.1 Channels

Micro-architectural side-channel attacks use data-dependent micro-architectural resources as channels for transmitting information stealthily. Specifically, the inner state of the micro-architectural resources is encoded with the information associated with the victim's program execution. Although this encoding does not affect the victim's program output, the state can be decoded by the attacker who accesses the same hardware and uses specific instructions to monitor the hardware state. Eventually, this enables the attacker to learn the victim's secret information.

To illustrate the concept, take the cache side-channel attack, such as Prime+Probe [5, 34, 56] as an example. In the Prime+Probe attack, the attacker preloads a specific memory address into the cache, therefore accessing to this address is a cache hit unless other addresses sharing the same cache set are loaded and evict this address from the cache. By waiting for the victim's execution and then testing whether this address is cached, the attacker can deduce whether the victim loads addresses into the same set. Based on how different address values are mapped into cache sets, the attacker can further recover a significant portion of the victim's address bits.

Over the years, various cache attacks have been created, in addition to Prime+Probe [10,

<sup>&</sup>lt;sup>1</sup>Note a side channel is different from a covert channel. In a micro-architectural covert channel, the sender and the receiver are both malicious parties who agree to use a micro-architectural resource to transmit data. Although the setting is similar, a side channel attack assumes a victim program that is beyond the attacker's control.

15, 35, 57, 58, 59, 60]. Many other micro-architectural structures that are exploited in similar manners, such as branch predictors [17, 18, 19, 20, 61], instruction decoders [62], micro-op caches [21], instruction scheduler [63], execution units [22, 64, 65, 66], Translation-Lookaside Buffers (TLBs) [16], data prefetchers [23, 24], DRAMs [67, 68], and many more. These channels can be further characterized by three factors:

#### Channel Duration

Based on how long the transmitted information remains inside the channel, we can roughly characterize micro-architectural side channels into two types, based on the duration:

- Ephemeral: Ephemeral channels are micro-architectural resources that exhibit observable data-dependent usage only during the instruction's execution. For instance, many execution units, such as multiplier [64, 65] and floating-point units [22] have data-dependent behavior (e.g., timing), which allows a side-channel attack to infer knowledge about the operand value based on their behavior. However, the behavior depends only on the operand of the currently executed instruction, not on the previously executed ones. Several other attack vectors, such as execution port contention [66] and cache bank conflict [69], are also ephemeral channels. Since the leakage from ephemeral channels is present for a short duration during the instruction's execution, it typically imposes strict requirements on the attacker, such as close proximity to the victim, and concurrent execution with the victim.

- Persistent: Persistent channels maintain the date-dependent effects of instructions even after they have retired, thus impacting instructions executed much later in the pipeline. One prominent example of a persistent channel is the processor cache: accessing the cache causes an irreversible change to the cache state, including the eviction of existing cache lines. Subsequent memory accesses to the evicted line will experience cache misses and longer access latency, from which one can infer the confidential memory access patterns. Secret information transmitted through persistent channels persists for an extended duration compared to ephemeral channels, which significantly relaxes the attacker's requirements. For instance, if the secret-dependent micro-architectural state change persists throughout a process context switch, the attack will not necessitate concurrent execution. However, certain resources such as TLB in many processors perform state sanitization when transitioning between different security domains, thereby mitigating the advantage of persistent channels.

#### Channel Location

When the attacker has only end-to-end measurements of the computational side effect of the victim's computation, e.g., through a remote timing attack, the physical location of the channel within a processor becomes irrelevant in terms of the attacker's proximity. However, in the co-location attack setting where the attacker typically needs to measure the channel state, the channel placement becomes crucial as it directly affects its exploitability. For example, several *intra-core* channels, like the branch predictor [19, 20, 61], micro-op cache [21, 70], and load-store unit [71], reside within the core pipeline. Therefore the attacker must be scheduled to the same core as the target victim program to observe the data-dependent usage of those channels.

Additionally, there are also micro-architectural resources shared between processor cores, such as the shared cache [7, 11, 15, 34, 35, 56, 57, 58, 72, 73], shared directory [60, 74], and on-chip interconnect [75, 76, 77]. By utilizing these *inter-core* resources as channels, the attacker is not limited to only the victim's core, and can instead launch the attack from other cores, which significantly improves the practicality and the effectiveness of the side-channel attack.

The requirement of the attacker's location can be further relaxed by *cross-processor* channels [78], which enables side-channel leakage across processors.

#### Channel Information

While various micro-architectural resources exhibit data-dependent behavior and serve as channels, they transmit different types of information related to the executed instructions. The information about the instruction *type* is naturally leaked by what execution units are used for the instruction, as well as other characteristics about the instruction itself, such as the execution timing, and whether or not it accesses the memory subsystem. Although the instruction type is typically not considered confidential, as we will explain next in Section 2.3.2, it can reveal secret control-flow decisions that lead to the execution of the current instruction.

The primary type of information exposed through the execution of instructions pertains to the *operand values* of the instructions. For instance, information about the source operand of floating-point instructions can be leaked by the latency of their execution [22]; the address operand of memory loads can be partially leaked via the accessed cache set or bank [5, 69]. The specific information leaked about the instruction's operand depends on the hardware implementation. In Prime+Probe attacks, for example, only the cache set bits from the

address operand of memory instructions are leaked. However, even the leakage of a limited number of operand bits can pose a significant threat to real-world applications, such as those involving cryptographic algorithms [79].

Another significant type of information that is commonly leaked through various identified channels is the *instruction's address*, also referred to as the *Program Counter (PC)* value [80]. Several hardware structures, including the instruction cache, branch predictors, micro-op cache, and hardware prefetchers, are directly accessed and updated based on the instruction's address as part of their functionality. This enables the side-channel attack to learn information regarding the instruction address based on their behavior [4, 17, 18, 19, 20, 21, 24, 70, 81, 82, 83, 84]. As later described in Section 2.3.2, acquiring knowledge about instruction addresses assists the attacker in deducing the program control flow, which contains sensitive information in many applications, such as cryptographic codes [33].

#### 2.3.2 Transmitters

As shown in Figure 2.1, a classic side-channel leakage starts with the victim's transmitter instructions operating using the secret information. These transmitter instructions will incur data-dependent behaviors to the exploited channels, which are later observed by the attacker. The transmitter instructions determine how the side-channel attack should be conducted and what secret information is collected through the attack. Therefore, information about the target transmitter instructions in the victim program is generally required for launching classic side-channel attacks.

Transmitter instructions are related to secret data through data flow or control flow. In other words, the transmitter instructions are either data-dependent on the secret, or control-dependent on the secret. We now use the following example in Algorithm 2.1 to explain these two kinds of transmitters.

Algorithm 2.1: A pseudocode example of the square-and-multiple algorithm for modular exponentiation, which is used by the RSA algorithm. Secret data are marked in red.

- Data-dependence: A transmitter instruction that is data-dependent on the secret has its source operands data-dependent on the secret. Information about the secret is leaked when this type of transmitter instruction interacts with channels that leak operand values. For example, consider line 3 of Algorithm 2.1. The condition of the branch instruction from this line has a clear data dependence of bit, which corresponds to bits of the private component. The branch instruction's execution requires branch predictor, which is a common channel for leaking branch predicate values [17, 18, 19, 20, 61].

- Control-dependence: For transmitter instructions that are control-dependent on the secret, the fact that they execute or not is decided by the secret. For instance, line 5 of Algorithm 2.1 has control-dependence of the secret exponent. By observing whether the instructions corresponding to line 5 execute, the attacker could learn each bit value. Note that in practice the attacker has various channel options for exploiting transmitters with control-dependence of secrets. For example, assume that a branch with a secret condition has two sides of different types of operations, or the same type of operations but different operand values. In those cases, the attacker can utilize specific channels for differentiating instruction types or operands, as described above. A more straightforward approach is to leverage channels that leak instruction addresses, such as the instruction cache [20, 81, 82, 83]., branch predictors [17, 18, 19].

#### 2.3.3 Receivers

In contrast to attacks like memory corruption attacks [13] where the attacker can conveniently read the victim's secret, side-channel attackers rely on carefully crafted receiver instructions to capture the victim's computational side effects. Although these side effects are not the actual target secret, they can be utilized to deduce the target secret through analysis.

The choice of receiver instructions is straightforward in remote attacks: the attacker employs primitives for measuring the side effect during their interactions with the victim. In a typical remote-timing attack, the attacker records the wall clock time when invoking and receiving responses from the vulnerable victim routine. The attacker would then use complex analysis techniques to extract the target secret [85]. The specific analysis methods utilized by the side-channel attackers are beyond the scope of this thesis.

In scenarios when the attacker co-locates with the victim, the attacker must include instructions in their receivers that use the intended hardware resources (channels). More importantly, these instructions must be properly parameterized so that their execution is influenced by the victim's transmitters through the channel behavior. As an example, in Prime+Probe cache attacks, the attacker aims to observe whether the victim accesses a specific cache set. Therefore, the attacker would normally incorporate memory loads in their receiver instructions to probe the same cache set. The attacker also includes measurement primitives to observe the execution of those instructions, such as timing the memory accesses in Prime+Probe attacks.

#### 2.4 SPECULATIVE SIDE-CHANNEL ATTACKS

The surge of speculative side-channel attacks (also referred to as speculative execution attacks), notably led by Spectre [4] and Meltdown [3] has opened up a new chapter of micro-architectural side-channel attacks, and greatly advanced our understanding of this type of attack. Speculative side-channel attacks overcome a major limitation of classic side-channel attacks where the attacker can only exfiltrate victim secrets that are consumed by the victim's transmitter instructions in a valid (retired) execution. In speculative sidechannel attacks, the attacker exploits the various hardware speculation mechanisms in today's high-performance processors, to transiently execute instructions (which are invalid execution due to mis-prediction). While speculative execution never affects program correctness as the invalid execution is eventually squashed once the misprediction is detected, it introduces major security problems: the attacker can leverage speculative execution to allow transmitter instructions to consume secret data that it would not consume in normal, non-speculative execution. Even though the execution is ultimately invalidated, the transient execution of transmitter instruction facilitates secret-dependent utilization of channels (such as processor caches), thereby leaking the secrets to the potential receivers. Since prediction and speculation are pure hardware optimizations, it is impossible for programmers to reason what data can be speculatively accessed and leaked.

Figure 2.1 (2) illustrates the process of speculative side-channel attacks. Speculative side-channel attacks leverage the classic side-channel attack flow "transmitter  $\rightarrow$  channel  $\rightarrow$  receiver" for transmitting the victim's secrets to the attacker. On the other hand, these attacks exploit hardware prediction and speculative execution to realize "secret  $\rightarrow$  transmitter" relationships that never appear in the normal program semantics.

**Algorithm 2.2:** A pseudocode example of the Spectre V1 [4] example, which has a branch followed by the access and transmitter instructions. secret data are marked in red.

As a demonstration, consider the original Spectre V1 attack, illustrated by Algorithm 2.2. The vulnerable code contains a branch, which will be mispredicted by the branch predictor after the attacker trains the predictor. The branch condition, cond, may take a significant amount of cycles to compute, thus giving sufficient time for transiently executing the instructions inside the branch block. The access instruction on line 3 transiently accesses a secret, and the subsequent transmitter instruction uses the secret value as the memory operand, therefore leaking the secret through channels such as cache [4, 86] or TLB [87].

A speculative side-channel attack typically requires three extra components beyond a classic side-channel attack: the predictor training code, a predictor, and a disclosure gadget which includes the combination of access and transmitter instructions. A previous survey work by Xiong et al. uses a similar framework for classifying speculative side-channel attacks [88]. We now discuss all three components in details.

#### 2.4.1 Predictor

There are various prediction mechanisms in modern processors that have been exploited for speculative side-channel attack purposes, which include:

- Branch prediction: Branch prediction is the most common hardware optimization that involves multiple hardware structures such as pattern history tables (PHTs, also called directional predictors), branch target buffers (BTBs), and return stack buffers (RSBs, also called return address stacks or RASs). All these structures have been the target of different attacks for generating misprediction. For example, the PHT has been exploited in the original Spectre V1 attack [4] and its derivatives [89, 90]; the BTB has been exploited in Spectre V2 attack [4] and its derivatives [91]; the RSB has been exploited in [92, 93].

- Memory address dependency prediction: Memory address dependency prediction, also

referred to as memory disambiguation, is another prediction mechanism widely used by high-performance processors to predict the dependency between memory loads and stores when their address operands are unavailable. This prediction mechanism allows speculative data flow between stores and loads, which motivates several speculative attacks such as Spectre V4 [84, 94, 95].

- Hardware prefetching: Differing from branch and memory dependency prediction, hardware prefetching does not lead to software instructions being speculatively executed. Instead, an activated hardware prefetcher will perform memory accesses that do not correspond to any software instructions. Attacks such as Augury [23] have found that in some processors, a hardware prefetcher can also be trained in a similar way as branch predictors and result in a similar leakage as the Spectre attack.

- Exception: Several existing attacks, such as the Meltdown attack [3] and ForeShadow [96, 97], are built on the observation that processors typically resolve exceptions at the retire stage. This allows the subsequent instructions to exploit the fault and perform operations that would otherwise be prohibited before the exception is resolved. So even though exceptions are fundamentally different from hardware predictions, it has a similar effect as predictions in terms of speculative execution attacks: code dependent on the instruction triggering the exception gets transiently executed.

# 2.4.2 Predictor Training Code

As Figure 2.1(1) shows, a successful speculative side-channel attack starts by utilizing predictor training code for training the hardware predictor into a state which produces desired misprediction for the attack. Depending on the targeted predictor structure, the predictor training code includes different instructions. For example, conditional branches are used to train PHTs, while jump instructions are employed for BTBs. In most attacks, the attacker exploits the sharing nature of hardware predictors to train the predictors using predictor training code within their own programs [3, 86, 92, 93, 95, 96, 97, 98, 99, 100, 101, 102]. However, this approach necessitates the attacker and the victim being co-located on the same processor core, and the exploited hardware predictor cannot adopt mechanisms that isolate the predictor state between the attacker and the victim. If these requirements are not satisfied, the attacker may resort to leveraging predictor training code available within the victim software routine, provided they can directly invoke such routines [4, 94]. Lastly, the predictor training code is not necessary for a successful speculative attack; the predictor state may correspond to a well-trained predictor state by pure coincidence.

# 2.4.3 Disclosure Gadget

Another key step in speculative execution attacks is the transient execution of the disclosure gadget, which includes access and transmitter instructions. The access instruction should transiently access the secret data by bringing it into the core pipeline, and a subsequent transmitter instruction consumes the secret and generates secret-dependent channel usage, such as cache access or data-dependent execution timing. Because the leakage must happen transiently (otherwise those instructions will be squashed before the secret-dependent channel usage is made), the attacker must create a sufficiently large *speculation window* for covering those instructions. For instance, in the Spectre Attack shown in Algorithm 2.2 where the access and transmitter instructions follow a branch, the attacker must induce a long latency for determining the branch condition, thus the access and transmitter instructions can finish their execution, and leak the secret through cache before the branch misprediction is identified. The transmission of secret information from the channel to the attacker through receiver instructions is identical to classic side-channel attacks.

In Spectre V1 and other variants, attackers exploit the access and transmitter instructions embedded within the victim code to extract the victim's secrets. However, many speculative attacks, represented by Meltdown, have showcased how access and transmitter instructions inside the attacker's code can also result in a similar effect [3, 96, 97, 99, 100, 101, 102, 103]. Ideally, processors should enforce strict isolation between distinct security domains to prevent attackers from accessing the victim's program data. Unfortunately, these attacks have found that real processors have implemented various optimizations that could temporarily violate the isolation during transient execution, which enables the attacker's access instructions to momentarily access and transmit the victim's data. For example, the original Meltdown attack demonstrated that in modern Intel processors, when a (potentially malicious) user program accesses kernel memory and triggers an exception, before the exception is handled at the retire stage of the faulting instruction, subsequent instructions can transiently consume the accessed kernel data, causing leakage of kernel data through classic side channels. Subsequent attacks like ForeShadow [96, 97], MDS [100, 101, 102], and others [103, 104, 105] exploit different conditions when speculative execution relaxes the isolation policies, such as when speculative data is in the L1 cache or in various on-chip buffers.

A speculative side-channel attack can also include a combination of a non-speculative access instruction and a speculative transmitter instruction as the disclosure gadget. However, this attack approach is relatively uncommon due to a major drawback compared to existing attacks with speculative access instruction. With a transiently-executed access instruction, data that would otherwise be inaccessible during normal execution can be transiently fetched

and leaked, which significantly enlarges the attack surface. This has been demonstrated originally by Spectre [4] and Meltdown [3] as they were able to leak the entire kernel memory from userspace.

#### 2.5 MITIGATIONS FOR CLASSIC SIDE-CHANNEL ATTACKS

Since the appearance of classic side-channel attacks such as cache attacks, researchers have proposed various software and hardware countermeasures to mitigate those attacks, which is the focus of this section.

## 2.5.1 Software Mitigations

Software mitigations cannot directly fix the vulnerable micro-architectural resources (channels). Instead, they focus on software elements that constitute the classic side-channel leakage, which are the transmitter instructions and the receiver instructions.

# Addressing Transmitters

Classic side-channel attacks start with the victim's transmitter instructions consuming secret data as their input operands, and the execution of the transmitters creates microarchitectural resource utilization that exhibits a correlation with the secret data. The strategy that software developers adopt to address the risk posed by transmitters is to introduce redundant program execution which obfuscates the measurement of channel usage.

For instance, consider the two scenarios depicted in Figure 2.2. In Algorithm 2.3, the memory access operation uses secret data in its address calculation (line 4), rendering it vulnerable to side channels that can divulge address access patterns, such as cache attacks [25]. To conceal the real target (secretIndex), as Algorithm 2.3 shows, one common approach is to perform a memory scan across all potential targets (all elements of publicData in the case of Algorithm 2.3) and only use the right data for subsequent computation [106, 107, 108]. This simple approach ensures that the memory access pattern no longer reveals information about the secretIndex. However, it comes at a significant performance cost of O(N) bandwidth cost for each access. One may assume that the attacker has no observability over the cache line offset bits, which holds for most cache attacks, and only access addresses that are multiples of cache lines away from the target address. This strategy is further challenged by more subtle attacks which are capable of leaking low-order address bits [66]. To address all these attacks that collectively reveal different parts of memory addresses, researchers resort to more

```

Algorithm 2.3: Memory access with a secret address operand. secretIndex could be leaked via cache side channels.

Input: array publicData of size N; secret index secretIndex

```

```

Output: returned value tmp

1 dummy ← publicData[0];

2 dummy ← publicData[1];

3 ... ...;

4 tmp ← publicData[secretIndex];

5 ... ...;

6 dummy ← publicData[N-2];

7 dummy ← publicData[N-1];

```

```

Algorithm 2.4: Branch with a secret predicate. cond could be leaked via observing the execution unit usage.

```

```

Input: integers a, b, c

secret branch condition cond

Output: returned value tmp

1 if cond then

2 | tmp ← a * b;

3 | tmp ← tmp + c

4 else

5 | tmp ← a * b;

6 | tmp ← tmp + 0

7 end

```

Figure 2.2: Two examples of how secret is leaked by transmitters taking secret input operands through micro-architectural side channels. Programmers may address this leakage with redundant operations, marked in blue, to obfuscate the data-dependent micro-architectural behavior.

strict security policies—such as memory trace obliviousness [109]—which require the memory address pattern to be independent (or oblivious) to any secret information. In fact, the problem of performing memory accesses with confidential addresses motivates the creation of Oblivious RAM [110, 111, 112, 113], which strives for achieving sub-linear bandwidth cost with the aid of some adversary-invisible data structures (such as position map in [114]). Nonetheless, these methods are rarely used in practice due to their performance degradation.

Algorithm 2.4 represents another common scenario when the secret control-flow decision is leaked through branches or other control-flow structures. In the original form, the *then* path includes one more addition than the *else* path, therefore a side-channel attacker who is capable of measuring the execution time of the branch body can easily deduce the branch decision. A simple countermeasure against this attack approach is to add a dummy addition (line 6 to balance both sides and ensure identical execution time. However, the fixed code remains vulnerable to other side-channel attacks, such as those that can observe the address sequence of executed instructions (at different granularity, such as page [115] or cache line [116]). The attacker may even learn the conditional branch direction directly by monitoring the behavior of the hardware branch execution unit [19, 20, 61]. To mitigate those attacks, software developers may adopt more aggressive code transformation techniques, such as restricting the secret-dependent control flow to the minimal observation granularity (cache/page) [117]. In high-security applications such as cryptographic libraries, a common practice is to eliminate secret-dependent branches by performing the worst-case amount of work [118].

The endeavors of programmers in search of side-channel-free programming techniques have

led to data-oblivious programming [22, 30, 106, 107, 114, 119, 120, 121, 122, 123, 124, 125, 126, 127, 128, 129]. Data-oblivious programming, also known as "constant-time programming" or "writing programs as circuits", aims to thwart micro-architectural side channels by ensuring secret-independent hardware resource usage. It provides a formal framework for adding redundant operations in code vulnerable to side channels, such as Algorithm 2.3 and 2.4. Despite its strong security guarantee, its significant performance overhead still impedes its practical adoption in real-world applications [118]. Moreover, the emergence of speculative execution attacks has raised concerns about the security of data-oblivious programming, which was originally designed to address classic side-channel attacks without considering out-of-order and speculative execution [30, 130, 131].

# Addressing Receivers

Preventing attackers' receiver instructions from measuring secret information through the channel provides another direction for countering micro-architectural side-channel attacks. Since any micro-architectural side-channel attack, regardless of the attacker's proximity to the victim, relies on analyzing the correlation between the measured computational side effects (e.g., timing) and target secrets, introducing inaccuracies in the measurement is considered an effective mitigation applicable to any micro-architectural side-channel attacks, including speculative attacks that still utilize classic side channels for secret transmission. Since most side-channel attacks leverage high-resolution timers, possible mitigations can be reducing the timing resolution, fuzzing, or completely disabling the timing source [132, 133, 134, 135, 136]. However, injecting noise or completely disabling the timing source is impractical in many circumstances, and will result in significant performance degradation [137]. Furthermore, subsequent attacks have been proposed to completely eliminate the side-channel attack's dependence on timers [36, 138, 139, 140, 141].

Considering that many micro-architectural attacks assume the attacker's physical proximity to the victim for the direct observation of the hardware resource usage, a straightforward approach is to assign the victim application exclusive ownership of an isolated core (to mitigate intra-core attacks) [142] or even an isolated processor (to mitigate cross-core attacks). However, as the current trend of building processors that are capable of running more concurrent workloads continues, these mitigation strategies come at the expense of higher performance costs. Researchers have also proposed to sanitize the victim's secret-dependent hardware state change, such as flushing the cache [5, 143] and the branch predictor state [144] when switching between security domains. While these solutions result in less performance impact, they offer a trade-off in terms of weaker security guarantees.

# 2.5.2 Hardware Mitigations

Micro-architectural side-channel attacks exploit security flaws in the hardware design, therefore incorporating defense strategies during the hardware design process should address the root cause of micro-architectural side channels. Additionally, hardware mitigations generally provide better software compatibility due to less involvement by the software. However, few of those hardware mitigations are implemented in real-world processors, since they usually introduce significant design complexity as well as non-negligible performance cost.

#### Secure Hardware Units

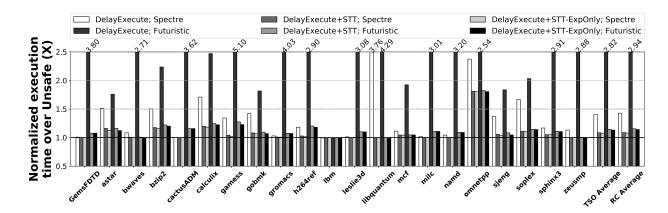

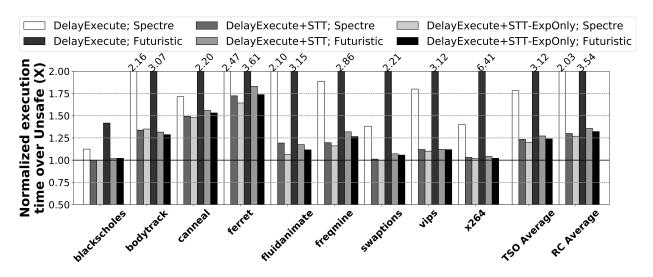

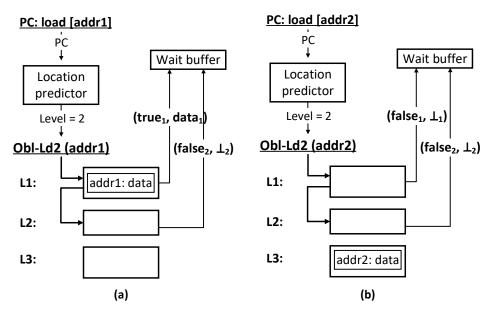

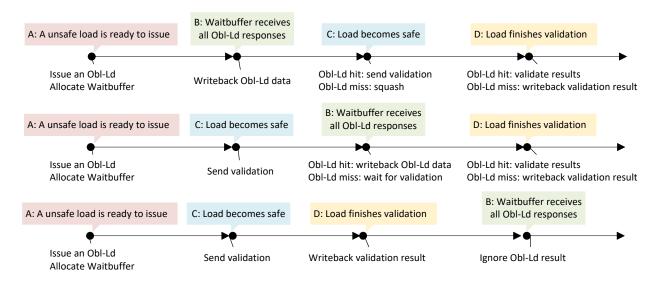

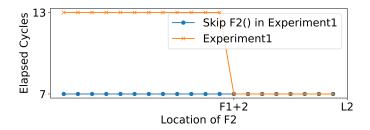

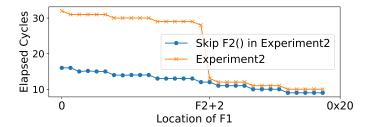

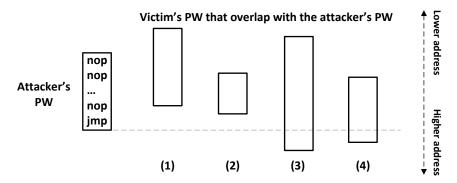

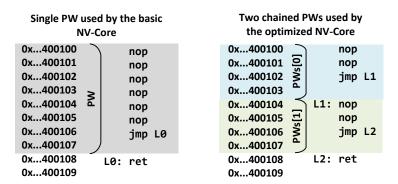

Most current hardware mitigations focus on hardening individual micro-architectural resources that induce side-channel attacks, such as caches, TLBs, branch predictors, etc. These resources are commonly shared by programs from distinct security domains, allowing potentially malicious programs to learn secret information from the hardware resource usage pattern of the victim program. Based on the cause of the information leakage, most existing solutions aim for achieving non-interference: the execution of a program cannot create secret-dependent hardware resource usage that can be observed by the execution of another program from a different security domain. To achieve non-interference, these solutions typically follow two different methodologies (some may aim at the best of both worlds):