$\bigodot$ 2022 Vikram Sharma Mailthody

#### APPLICATION SUPPORT AND ADAPTATION FOR HIGH-THROUGHPUT ACCELERATOR ORCHESTRATED FINE-GRAIN STORAGE ACCESS

BY

#### VIKRAM SHARMA MAILTHODY

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois Urbana-Champaign, 2022

Urbana, Illinois

Doctoral Committee:

Professor Wen-mei Hwu, Chair Professor Sanjay Patel Professor Deming Chen Dr. I-Hsin Chung, IBM Research

## Abstract

Accelerators like Graphics Processing Units (GPUs) have become popular compute devices for HPC, cloud, and machine learning applications because of their compute capabilities and high memory bandwidth. However, GPUs and other accelerators still live within the confines of their modest memory capacity and rely on the inefficient software stack running on the CPUs to orchestrate access to data storage. This CPU-centric data orchestration is well-suited for GPU applications with parallel computation patterns that are flat and regular in nature, like dense neural network training. Unfortunately, many emerging workloads, such as graph and data analytics, recommender systems, or graph neural networks require fine-grain, data-dependent sparse access to storage. The CPU-centric data orchestration of storage accesses is unsuitable for these applications due to high CPU-GPU synchronization overhead, I/O traffic amplification, and excessive CPU software bottlenecks.

To overcome these limitations, this work analyzes and shows the feasibility of using GPUs to orchestrate high-throughput fine-grain direct access to storage for emerging workloads. We propose, implement, and evaluate the design of a cost-effective system architecture called BaM (Big Accelerator Memory). BaM capitalizes on the recent improvements in latency, throughput, cost, density, and endurance of solid-state storage devices and systems to realize another level of the accelerator memory hierarchy. BaM is an accelerator-centric approach where GPU threads can identify and orchestrate on-demand access to data where it is stored, be it in memory or storage, without the need to synchronize with the CPU. This significantly decreases the CPU-GPU synchronization overhead, avoids CPU software stack inefficiency, minimizes I/O amplification, and enables GPU programmers to treat storage as memory.

However, naively running applications on BaM does not result in performance and efficiency benefits. As BaM essentially extends the accelerator memory hierarchy to the storage, favorable access patterns are needed for BaM to reach its full potential. This is because, on the one hand, BaM requires coalesced accesses for extracting high-throughput out of its cache, while on the other hand, the BaM I/O stack requires many concurrent I/O requests to hide the storage access latency. These conflicting requirements create a design dilemma, motivating the set of sophisticated optimization techniques and application adaptation strategies that allow applications to achieve peak performance on BaM.

The proposed techniques, cache-line aware parallel work assignment, and on-demand implicit tiling methods are generalizable across a wide range of data structures and emerging applications. Using these optimizations and application adaptations, we show that BaM is a viable, much less expensive alternative to the existing DRAM-only and other state-of-the-art CPU-centric solutions. Overall, this dissertation proposes a design of a system capable of performing GPU orchestrated storage access to extend the GPU's effective memory capacity and provides a set of generalizable application adaptations that enables application developers to maximize the performance, cost, I/O efficiency, capacity scalability, and simplified software development for emerging workloads, even without additional hardware support. With BaM, the user gets the teraflops of GPU compute capability and terabytes of GPU accessible memory at a low cost. To my parents, and family, for their unwavering love and support.

# Acknowledgments

I want to express my gratitude to my advisor, Professor Wen-mei Hwu, for bringing me to UIUC and for being an exemplary role model for me in every way. This includes his vision, curiosity, optimism, intellectual integrity as a researcher, patience, dedication, efficiency as a teacher and industry leader, and compassion as a person. Whatever the situation, Professor Hwu is always ready to listen and offer assistance. I'm here because of his persistence, wisdom, mentorship, trust, and undivided attention. I will forever be grateful for the advice, guidance, insights, and assistance I received as his student. I also want to thank Sabrina Hwu for looking after us like one big family along with Prof. Hwu!

I want to thank my committee for their insightful comments and interactions. I would also like to thank Professor Sanjay Patel for his advice and friendship, which immensely aided my professional growth as a researcher. I have never met anyone so busy yet always willing to listen and offer advice on any random topic. Additionally, I thank Professor Deming Chen for providing the thoughtful and responsive feedback and for going above and beyond the call of duty. I cannot express enough gratitude to Dr. I-Hsin Chung, a collaborator from IBM Research and a mentor who never stopped helping me when I was stuck. He shared critical industrial perspectives that significantly shaped this thesis that would have easily been missed in academia.

Next, I would like to thank my academic twin, Zaid Qureshi, for enduring me and supporting me in every possible way. He has been a friend and inspiration since day one of my Ph.D. and has profoundly influenced me professionally and personally. He is someone who can maneuver around most obstacles and helped me to rethink what is possible. And of course, not to forget our constant *noisy* interaction with jalapeno effects made me feel not alone during the Ph.D. journey. Our unique collaborative research style has immensely impacted both of our works. I would also like to thank my collaborators, especially, Professor Jian Huang, Professor Andrew Miller, Professor Christopher Fletcher, Professor Jinjun Xiong, Professor Rakesh Nagi, Professor Nam Sung Kim, Professor Saugata Ghose, Professor Scott Mahlke, Professor Josep Torrellas, and many others from academia, Dr. William Dally, Dr. Micheal Garland, Dr. Isaac Gelado, Dr. CJ Newburn, Dr. Eiman Ebrahimi, Dr. Hubertus Franke, Dmitri Vainbrand, Brian Pan, and many others from the industry. Their views shaped my thinking and helped me make an impact on the real-world problems that matter at scale.

I want to thank the IMPACT Research Group and its members (past and present) for their feedback and companionship throughout the journey from day one. Talking to these folks, socializing, and making jokes were among the best experiences during my stint with this group! A special shout out to Professor Izzat El Hajj, Dr. Carl Pearson, Dr. Simon Garcia De Gonzalo, Dr. David Min, and Professor Sitao Huang for being personal role models and mentors during my Ph.D. I extend my gratitude to Te-Chia Kao, Marie-Pierre Lassiva-Moulin, and Andrew Schuh, for their positive energy and for making our life simple with less paperwork. I also extend my gratitude to the ECE, CS, and CSL staff and faculties for their help and assistance. Special thanks to Taryn Smith for proofreading this document.

I would like to thank my friends and mentors, including Umur Darbaz, Kartik Hegde and Sneha Bhat, Sidharth Gupta, Satwitk Tejaswi, Edward Richter, Karthik JVN, Ahmed Abulila, Varun Kelkar, Ranvir Rana, and many more who made every day special to live and cherish.

I am not who I am without my parents, my brother and his family, and my fiancé and her family. My parents, Chandrakala Delampady and Jayarama Sharma Mailthody, made me realize my potential whenever I was stuck or confused. I admire the patience, optimism, encouragement, support, and unlimited love they keep showering throughout my life.

Lastly, I thank my funding agencies and research grants that made this thesis possible, especially the IBM-C3SR research center and NVIDIA research. I would also like to acknowledge the valuable insight and donations received from several key stakeholders, including Intel, Samsung, Phison, H3 Platform, Broadcom, and the University of Illinois. Especially discussions with Brian Pan, Jean Chou, Jeff Chang, Yt Huang, Annie Foong, Andrzej Jakowski, Allison Goodman, Venkatram Radhakrishnan, Max Simmons, Michael Reynolds, John Rinehimer, In Dong Kim, Young Paik, Jaesung Jung, Yang Seok Ki, Jeff Dodson, Raymond Chan, Hubertus Franke, Paul Crumley, and several others have been fundamental for this work to come to fruition. Vikram is partly supported by Joan and Bahl Fellowship and Dan Vivoli Endowed Fellowship during his Ph.D. This work is also partly supported by the IBM-ILLINOIS Center for Cognitive Computing Systems Research (C3SR) - a research collaboration as part of the IBM AI Horizons Network, and by the IBM-ILLINOIS Discovery Accelerator Institute (IIDA).

# Table of Contents

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                     | 1                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Chapter 2Background                                                                                                                                                                                                                                                                                                                                                                        | $5 \\ 5 \\ 6 \\ 7$                     |

| 3.3 GPU Accelerated Data Analytics                                                                                                                                                                                                                                                                                                                                                         | 8<br>8<br>10<br>12<br>14               |

| <ul> <li>4.1 I/O Amplification Problem With Proactive Tiling</li></ul>                                                                                                                                                                                                                                                                                                                     | 15<br>15<br>17<br>19<br>19<br>20<br>22 |

| Chapter 5       BaM: Enabling Fine-grain High Throughput GPU-Orchestrated         Access to Storage       2         5.1       BaM Vision And Design Goals       2         5.2       BaM System Overview       2         5.3       The Design Of A BaM Prototype       2         5.4       BaM I/O Stack Performance       3         5.5       BaM Cache Study Using Microbenchmark       4 |                                        |

| 6.1 BaM's Design Dilemma: The Problem                                                                                                                                                                                                                                                                                                                                                      | 46<br>47<br>51                         |

| 6.3 Regularizing Irregular Workloads In BaM                |

|------------------------------------------------------------|

| 6.4 Summary                                                |

| Chapter 7 End-to-end Application Case Studies              |

| 7.1 Performance Benefit Of BaM For Graph Analytics         |

| 7.2 I/O Amplification Benefit Of BaM For Data Analytics 94 |

| 7.3 Programming Simplicity Of BaM For Regular Workloads 98 |

| 7.4 Summary                                                |

| Chapter 8 Future Work And Expected Impact                  |

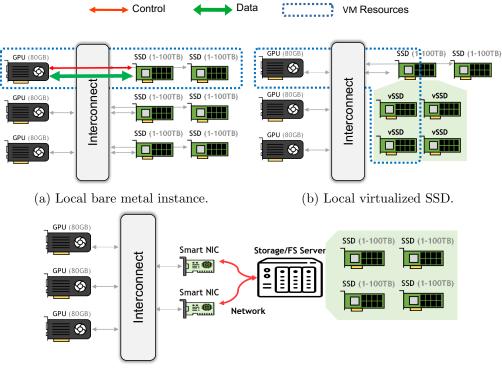

| 8.1 BaM Virtualization And Sharing For The Cloud 102       |

| 8.2 Work Efficiency Optimization for ODT technique 105     |

| 8.3 Future Of BaM System Software Stack                    |

| 8.4 Hardware Changes For BaM                               |

| 8.5 Additional Applications                                |

| 8.6 Expected Impact                                        |

| Chapter 9 Related Work                                     |

| 9.1 Optimized CPU-centric Model                            |

| 9.2 Prior Attempts Of The Accelerator-centric Model        |

| 9.3 Hardware Extensions                                    |

| 9.4 Using SSDs As CPU Memory                               |

| Chapter 10 Conclusion                                      |

| References                                                 |

# Chapter 1

# Introduction

After more than a decade of phenomenal growth in the compute throughput and memory bandwidth [1,2], GPUs have become popular compute devices for HPC and machine-learning applications and are proving to be effective general-purpose accelerators. Emerging high-value data-center workloads such as graph and data analytics [3–9], graph-neural networks (GNNs) [10, 11], and recommender systems [12–16] can potentially benefit from the compute throughput and memory bandwidth of GPUs. These applications access massive datasets organized into array data structures whose sizes typically range from tens of GBs to tens of TBs today and are expected to proliferate in the foreseeable future.

Storing these datasets as in-memory objects enables applications to naturally and efficiently process the data. However, GPUs and accelerators still primarily live within the confines of their modest memory capacity and are still controlled by the bulky software stack of the CPUs. The memory capacity of GPUs, despite a  $53 \times$  increase from that of G80 to A100, is only 80GB, far smaller than the required capacity to accommodate the entire datasets of these workloads. Several alternatives have been introduced to address the GPU memory capacity problem.

First, some current state-of-the-art approaches rely on the CPU user/OS code to proactively partition the datasets into chunks and orchestrate the storage access and data transfers of these chunks into the GPU memory for application processing [14–24]. Second, some prior work relies on memory-mapped files and GPU page faults to reactively transfer data on demand whenever the application attempts to access data not present in GPU memory [25–28]. This thesis refers to both proposals as a *CPU-centric* approach.

The CPU-centric approach of computing works well for classical GPU applications with parallel computation patterns that are flat and regular in nature, like, dense neural network training or matrix multiplications. Unfortunately, for emerging workloads, where the data lookups are increasingly becoming on-demand, data-dependent, and sparse, neither of these CPUcentric approaches provide meaningful performance, efficiency, and cost benefits. Our in-depth analysis of these CPU-centric approaches shows that they cause excessive CPU software bottlenecks and CPU/GPU synchronization overheads, resulting in poor performance (See §4).

To overcome such inefficiencies in the CPU-centric approaches, some stateof-the-art solutions use the host memory [5], whose capacity typically ranges from 128GB to 2TB today, or pool together multiple GPUs' memories [16] to host the entire datasets of emerging workloads. We will refer to the use of host memory or pooling of multiple GPUs memory to extend the GPU memory capacity as the *DRAM-only* solution. While DRAM-only solution has become a common practice in industry and academia, extending the host memory or memory pooling from multiple GPUs to the level of tens of TBs is a costly proposition. For instance, an application requiring 10TB memory capacity would require 128 NVIDIA A100-80GB GPUs. Regardless of which memory, CPU DRAM expansion, or the pooled GPU is used to host these datasets, data must still be pre-loaded from storage into the extended memory, and not all data might be used due to conditions only known during run-time computation.

In this dissertation, we analyze and prove the feasibility of performing highthroughput fine-grain direct access from accelerators to storage for emerging workloads. We propose, implement, and evaluate the design of a cost-effective solution called BaM (Big Accelerator Memory). BaM capitalizes on the recent improvements in latency, throughput, cost, density, and endurance of solid-state storage devices and systems to realize another level of the accelerator memory hierarchy. BaM moves the needle in accelerator-initiated storage access significantly and comprises a storage driver stack to provision storage I/O queues and buffers in the GPU memory, a high-throughput cache for exploiting data reuse, and equips with a high-level abstraction to enable GPU self-orchestrated storage access.

BaM distributes and parallelizes the cache management across GPU threads and enables application threads in userspace to find data in parallel without relying on the traditional centralized authorities like operating system page-fault handlers. In BaM, GPU threads can identify and orchestrate ondemand accesses to data where it is stored, be it in memory or storage, without the need to synchronize with the CPU, significantly minimizing I/O amplification and enabling GPU programmers to think of storage as memory.

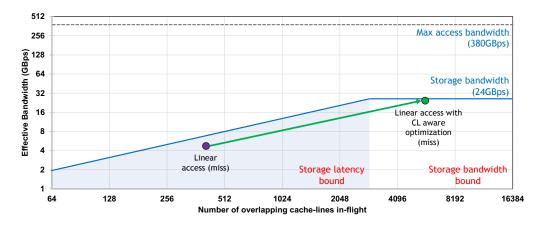

However, naively running applications on BaM *does not* result in performance and efficiency benefits. As BaM essentially extends the accelerator memory hierarchy to the storage, favorable access patterns are required for BaM to reach its full potential. This requires embracing two fundamental yet conflicting requirements. Essentially, on the one hand, we need coalesced accesses to conserve the available bandwidth of the BaM cache, while on the other hand, the BaM I/O stack and storage requires many overlapping concurrent I/O requests to hide the storage access latency. However, having coalesced accesses in the BaM cache minimizes the number of I/O requests submitted to the storage and thus cannot hide the latency!

To address this design dilemma, a set of sophisticated optimization techniques and application adaptation strategies are proposed to achieve peak performance out of BaM. The ideal access pattern should make use of BaM resources perfectly and should adhere to the following set of guidelines: (1) it should generate a large number of overlapping concurrent I/O requests to tolerate the long latency of storage access, (2) it should maximize the achievable bandwidth from BaM cache and the available I/O bandwidth, (3) it should be general and applicable to a class of applications and yet not degrade the performance when the application data fit in the GPU memory and (4) it should ultimately achieve good application level performance.

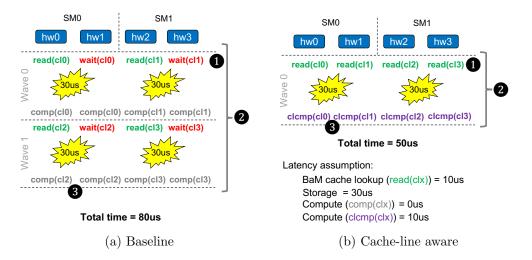

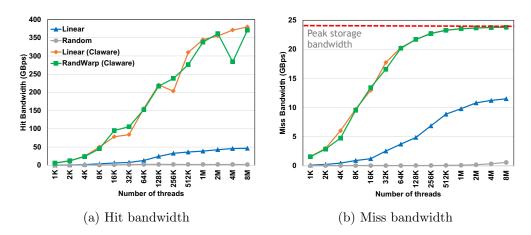

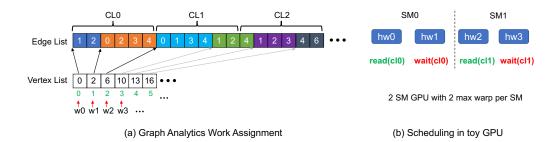

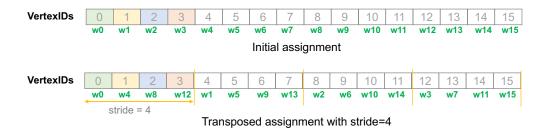

To this end, we propose the cache-line aware work assignment, a simple generalizable work assignment-based optimization that meets the above goals for all studied emerging workloads. The key idea of cache-line aware work assignment is to map each warp (or a thread block) to work on cache-line data in a manner that minimizes the contention when accessing BaM metadata and also generates a sufficiently large number of concurrent I/O requests to saturate the BaM storage stack.

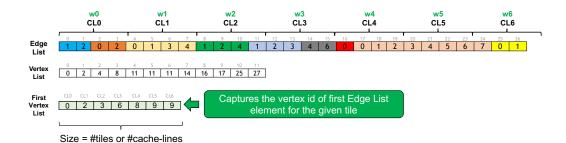

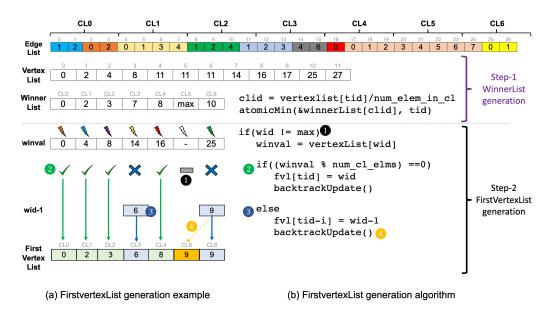

Although the cache-line aware work assignment provides a remarkable performance boost over naively BaM implementation, it may not be able to secure peak performance out of BaM. Thus, we discuss the limitations of this optimization in the context of graph analytics workload and then propose a novel application adaptation technique called "on-demand implicit tiling (ODT)" to perform efficient computation on Compressed Sparse Row (CSR) data-structure. In the ODT technique, each warp works on a tile of data instead of the traditional vertex-centric approach such that each loaded tile is optimally reused while also exploiting the GPU's massive parallelism to generate many concurrent I/O requests to hide the memory access latency. We show that the ODT technique regularizes the irregular accesses pattern of CSR data structure and maximizes the performance achievable out of the BaM system.

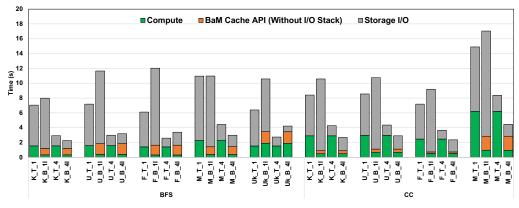

We then apply these optimizations and application adaptations to several emerging workloads across multiple datasets, SSD types, and I/O sizes and show that BaM is a viable, much less expensive alternative to the existing DRAM-only and other state-of-the-art CPU-centric solutions. For example, for graph analytics workloads, known to be notoriously hard to achieve good performance due to random memory access, BaM, with these optimizations, provide on-par or better performance over the current state-of-the-art host-DRAM only solution and is only  $4.27 \times$  slower than the GPU-HBM solution. We also show that the proposed optimizations are universal and improve or retain the same level of performance when the dataset fits within the GPU-HBM memory. And these performance benefits are extendable to other data-dependent workloads like the data-analytics where BaM can achieve up to  $5.3 \times$  speed up over the host DRAM-only solution. Lastly and more importantly, BaM is the only system that can scale beyond 100TB capacity at a reasonable cost and yet provide simplistic abstractions for programmers to work with large datasets.

Overall, this dissertation proposes a design of a system capable of performing GPU orchestrated storage access to extend the GPU's effective memory capacity and provides a set of generalizable application adaptations that enables application developers to maximize the performance, cost, I/O efficiency, capacity scalability and simplified software development for emerging workloads, even without any additional hardware support. With BaM, the user gets the teraflops of GPU to compute capability and terabytes of GPU accessible memory at a low cost. We believe BaM is the significant step in building accelerator-initiated access to storage and opens up a pandora's box of research questions to answer, both in hardware and software. We also hope BaM enables ground-breaking research ideas and applications that cannot execute with current systems.

# Chapter 2

# Background

This chapter provides a comprehensive overview of the technologies and concepts needed to understand the thesis. This chapter covers a high-level overview of the GPU programming model and architecture, GPUDirect technology, and relevant details of NVMe specifications.

### 2.1 GPU Programming Model and Architecture

In this section, we briefly describe the relevant aspects of the GPU architecture and the NVIDIA CUDA programming model that are required to understand this thesis. Although this section discusses assuming the CUDA programming model, the fundamentals of GPU architecture and programming model remain consistent across different vendors. The GPU architecture consists of many streaming multiprocessors (SMs) connected to tens of gigabytes of high bandwidth global memory. Each SM supports up to 2048 threads, tens of kilobytes of fast registers, and tens of kilobytes of scratchpad memory. With CUDA, a GPU programmer can launch a compute kernel on the GPU with thousands to millions of threads organized into thread blocks. The GPU schedules thread blocks on the SMs as the resource constraints permit. Once a thread block is scheduled on an SM, it remains there until all threads in the thread block have finished their execution. Threads in a thread block can synchronize and share data through a fast scratchpad memory, referred to as shared memory.

An SM further divides a thread block into warps, consisting of 32 threads. The SM uses the threads in a warp as the unit of work to schedule on the cores of the SM. An SM can coalesce the memory accesses of a warp if its threads access the same cache-line. This enables the SM to generate larger and fewer memory requests, optimizing the memory bandwidth utilization of the GPU. The SM hides the latency of memory and computes operations in warps by preempting them with other warps on the SM that are ready to execute. Threads executing on parallel SMs help hide the latencies experienced by anyone SM. As a result, GPUs have the hardware resources needed to provide high throughput for applications that exhibit a massive amount of fine-grain data parallelism.

### 2.2 GPUDirect Technology

GPUDirect is a set of features available in modern GPU architecture that allows peer-to-peer communication between two mapped device memory regions. NVIDIA introduced the GPUDirect RDMA technique in 2011 with Kepler architecture and CUDA 3.1 to accelerate data movement between the third-party PCIe devices and the GPU [29, 30]. With GPUDirect RDMA, the data transfer between a peer device and the GPU does not have to go through bounce buffers in the host memory, thus reducing latency and CPU overhead. Several prior works have used this technique to implement efficient data transfer from storage to the GPU [18–20, 22, 31]. The most recent attempt in this segment that is noteworthy is GPUDirect Storage [17] product from NVIDIA and similar efforts from AMD in the RADEON-SSG product lines [32].

However, the GPUDirect RDMA feature does not provide triggering control path modifications to the GPU. To address this, GPUDirect Async, a new feature introduced in CUDA 8.0 (2017), enables the GPU to trigger and synchronize with the peer devices by memory-mapping the third-party device BAR space within the CUDA address space. Transactions occurring with GPUDirect Async trigger memory-mapped I/O (MMIO) requests to the peer device enabling reduced involvement of the CPU in the critical path in application execution. Prior work has used this technique to interface with the network cards and communicates with remote GPU or storage [29, 30].

#### 2.3 NVMe Queues

The NVMe [33] protocol is the latest standard defined by the industry to enable high-throughput access and to provide virtualization support for both server and consumer-grade SSDs. NVMe protocol allows up to 64K parallel submission (SQ) and completion (CQ) circular serial queues, each with 64K entries per device. In practice, today's NVMe SSDs support much fewer (~ 128) and smaller (~ 4K entries) queues. The NVMe device driver allocates a pool of buffers in the memory for use by the DMA engine of SSD devices for read and write requests. These queues and buffers traditionally reside in the system memory in the CPU-centric model.

An application requesting storage accesses causes the driver to allocate a buffer from the I/O buffer pool for the request and enqueue an NVMe I/O command at the tail of an SQ with a unique command identifier. The driver then writes the new tail value to the specific SQ's write-only register in the NVMe SSD's BAR space, i.e., it rings the queue's doorbell. For improved efficiency, a driver can ring the doorbell once after enqueueing multiple requests into an SQ.

For a read request, the SSD device controller accesses its media and delivers the data into the assigned buffer using its DMA engine. For a write request, the SSD device controller DMAs the data in the buffer into its media. Once a request is serviced, the SSD device controller inserts an entry into the CQ. When the host driver detects that the CQ entry for a command identifier is in place, it retires the request, frees up the space in the queue, and buffers for the request. The CQ entry also notifies the driver of how many entries in the SQ are consumed by the NVMe controller. The driver uses this information to free up space in the SQ. The driver then rings the CQ doorbell with the new CQ head to communicate forward progress. An SSD device can efficiently insert CQ entries for multiple requests in one transaction.

# Chapter 3

# Emerging Large Scale Applications

We discuss the key trends witnessed in the high-value data center applications and the system requirements for their efficient execution. This chapter covers three main types of workloads: graph analytics, GPU accelerated databases, and recommender systems. However, BaM can provide performance and cost benefits for several emerging applications such as graph neural network workloads but are not covered in this thesis.

#### 3.1 Graph Analystics

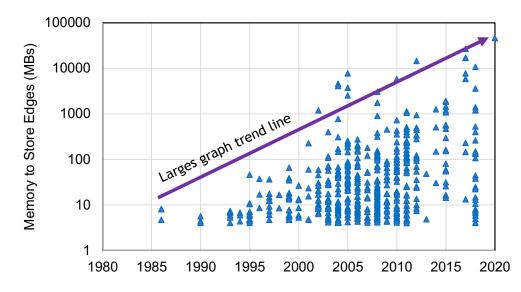

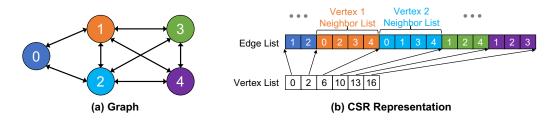

Graph workloads are becoming increasingly common in various analytics applications such as social network analysis, recommender systems, financial modeling, bio-medical applications, graph database systems, web data, geographical maps, and many more [3,7–9,34–41]. A recent survey by the University of Waterloo [34] finds that many organizations use graphs for various applications that usually consist of billions of edges and consume hundreds of gigabytes of storage. Figure 3.1 shows the trends in memory required for executing graph analytics workload over time based on one dataset collection: Suite sparse dataset [35]. For efficient storage and access, graphs are stored in a compressed sparse row (CSR) data format as it has low memory overhead. In the CSR format, a graph is stored as the combination of a vertex list and an edge list, as shown in Figure 3.2. Even with CSR data format, significant graph datasets can far exceed the capacity of today's GPU memory.

Graph traversal algorithms are fundamental primitive operations performed on a graph to understand its properties. The most common graph traversal algorithms are bread-first-search (BFS), connected components (CC), page rank (PR), and single source shortest path (SSSP). These algorithms form

Figure 3.1: Memory required for executing graph analytics workload over time.

Figure 3.2: An example graph (a) and the graph CSR representation (b) in memory. As shown in (b) each vertex has variable size neighbor list.

the basis of many higher-level algorithms and libraries [5,42–45]. Because of the massive parallelism available in graphs algorithms, these graph traversal algorithms are often accelerated using GPU [3,5,39,40,46–49].

In an optimized GPU implementation [5] of these algorithms for external I/Os, each GPU warp is assigned to a node being visited in the current iteration, where all threads in the warp collaboratively walk through the node's neighbor list. This is particularly true for applications such as BFS and SSSP. In the case of CC and page rank implementations, a similar assignment as BFS is followed, except that the application starts by examining all the nodes in the graph. Irrespective of the algorithm, each thread accesses a fine-grain data value (usually 4B or 8B, depending on the data type used to represent the graph) from the edge list for a given vertex. Since these accesses are data-dependent in nature, the access pattern becomes unpredictable.

#### 3.2 Recommender Systems

Recommender systems are ubiquitous across online retailers and social media companies as they drive their sales [12,14,15,50]. Recommender systems aim to predict the user's interests, determine to rank and click through-rates and recommend product items that are likely interesting to the users.

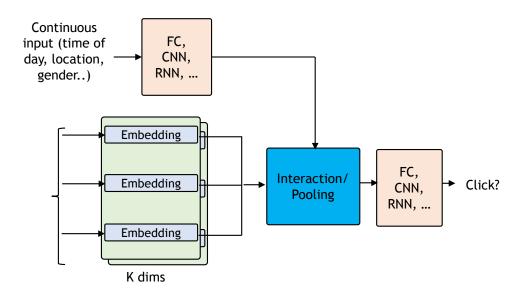

Typical deep learning-based recommendation models (DLRM) comprise sets of fully connected layers and embedding tables. Figure 3.3 shows a high-level architecture of a DLRM system. The system takes two sets of inputs: dense and sparse feature vectors. Dense feature vectors represent continuous or numerical features extracted from the user-specific profile. Examples of dense feature vectors are embedding vectors extracted for user age, name, or gender. On the other hand, sparse feature vectors or categorical features are a collection of embedding tables describing user interaction with different entities in the platform. Some examples of these entities are a list of movie names, their genre, and production companies. Each entity has a unique embedding table, and each entry in the embedding table has a unique embedding vector extracted using natural language processing models.

Dense feature vectors are directly fed into various types of multi-layer perceptron (MLP) such as Fully Connected (FC) layers, CNNs, and RNNs, as shown in Figure 3.3. To handle categorical features, embedding is mapped to form a dense representation in abstract space (reduction operation). During this step, each embedding lookup can be either a one-hot vector or a weighted combination of multiple embedding vectors [12]. This is followed by a second-order interaction computation across different features by taking a dot product between all pairs of embedding vectors and processing dense feature vectors in a batch. The interaction layer captures the cross relationship between two distinct dense and sparse feature vectors in latent space, avoiding the cold start problem<sup>1</sup>. The output of the pairwise interaction layer is fed to a top-level MLP or fully connected layer to compute the likelihood of a click between the user and the item.

DLRM models are fundamentally limited by the memory capacity available in the GPUs [14, 16]. The total number of parameters in DLRM models

<sup>&</sup>lt;sup>1</sup>Traditional matrix factorization techniques cannot capture unseen data points causing cold start problem. For example, a new movie that has not been rated by anyone yet, cannot be recommended to the user.

Figure 3.3: Model architecture of modern DLRM recommender systems.

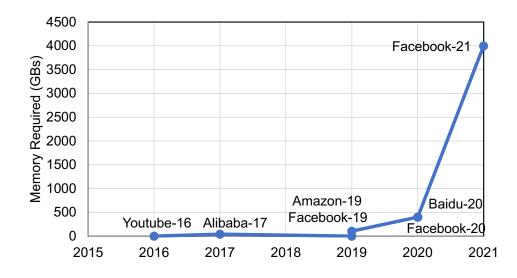

tends to be very large, going up to trillions. This is because large embedding tables help disambiguate the effect of different entities, thus increasing the accuracy of prediction in recommendation models [51]. During the datadependent lookup operation, visibility to entire embedding tables is needed as it is not possible to determine what data will be accessed when. Moreover, these models are trained frequently, usually every day, to capture the latest trending articles on the platform. This adds new entries in the embedding table over time, increasing the model capacity requirement. As new entities get created to capture new relationships between entities, additional sparse embedding tables are created and added to the model, further increasing the model capacity. Because of these, the number of parameters in the DLRM model is growing at an unprecedented rate as shown in Figure 3.4<sup>2</sup>. A trillion scale DLRM model constitutes up to 4TB of memory capacity requirement, assuming each parameter is a four-byte data type.

Besides memory capacity requirements, DLRM models exhibit sparse access patterns to the categorical embedding tables during the lookup operation. A *visited* bit vector is stored per entity to capture user interactions as the user may not have interacted with all the available entities on the platform. This bit vector is later used while performing sparse embedding lookup for the specific user in the DLRM model. Although the access pattern

$<sup>^{2}</sup>$ The analysis assumes each parameter consumes four bytes for data representation.

Figure 3.4: Trends in memory required for executing recommender systems workload across different companies.

is sparse, they exhibit power-law distribution when accessing the tables in memory [16]. This is because certain items are highly connected or occurring, resulting in frequent access. In addition, the access granularity of each request can vary depending on the DLRM model. The access granularity is equal to the embedding vector size of the given table and varies from 4B to up to 2KB in existing DLRM models [16,52].

#### 3.3 GPU Accelerated Data Analytics

Data analytics is the third most popular emerging workload of interest. The datasets used in data analytics typically consist of billions of records and tens or hundreds of metrics per record collected over a period of time. Data scientists analyze this massive amount of raw data to understand trends and metrics that would otherwise be lost in the mass of information. Data analytic workflows that rely on CPUs to load, filter, and manipulate data and perform analysis are slow and cannot exploit the massive data-level parallelism in these workflows. To address this, GPU accelerated analytic data pipelines such as NVIDIA RAPIDS framework [6] are used to execute queries on large datasets to generate meaningful insights from the data.

In RAPIDS, the GPU operates on DataFrames that provide a tabular view of the data, where there is a row per data record and columns for the various

Figure 3.5: Data frame representation of the NYC taxi ride dataset with NVIDIA RAPIDS.

metrics per record. Figure 3.5 shows an example DataFrame representation of the NYC taxi ride dataset with RAPIDs [53]. The dataset consists of 200GB of encoded data organized as 1.7B rows and 49 columns stored in the Optimized Row Columnar (ORC) format [54] supported by RAPIDS [6]. The rows are trip records from 2009 to 2021, and the columns specify aspects of the trip such as pickup location, drop location, payment type, trip distance, taxi company, start and end times, etc. As Todd Schneider puts in his blog [55], "Taken as a whole, the detailed trip-level data is more than just a vast list of taxi pick up and drop off coordinates: it's a story of New York." This is because the dataset addresses several questions a data scientist might have with respect to trip data for NYC.

Suppose we ask the question "Q1: What is the average total cost per mile for trips with at least 30 miles?". As the dataset has almost two billion rows and exceeds the GPU memory capacity, the programmer must process the data in smaller row groups that fit in GPU memory by (1) finding and loading each row group (i.e., tile) into the GPU memory, (2) performing the query on the GPU over the row group, and (3) aggregating results across row groups. During query computation over the row group, the trip distance column of the row group is scanned, and for trips that meet the criteria with a trip distance of at least 30miles, the total amount of the corresponding total amount array element must be aggregated. This results in sparse data access to various locations in the dataset.

Moreover, the query can be extended to answer more complex questions such as: "Q5: What is the average % mile the driver makes for trips with at least 30 miles?". To answer this query, we need four more data-dependent metrics from the dataset, and for each metric added, we can create a new intermediate query. We have to add the surcharges (Q2), hail fee (Q3), tolls (Q4), and taxes (Q5) metrics to get the penultimate query. To generate the final result, the query must perform selective column filtering with each new data-dependent metric.

Thus, the queries executing data analytics applications are data-dependent, requiring fine-grain access to the dataset. As the user dictates the sparsity (in this example, controlled by the condition criteria of 30 miles), different sparsity will result in a different result. Thus these requirements require data-dependent accesses, and what data requires to be fetched can only be determined at the query-execution time.

#### 3.4 Summary

To summarize, emerging high-value data-center workloads such as graph and data analytics [3-6, 53], and recommendation systems [12-16] can potentially benefit from the compute throughput and memory bandwidth of GPUs. However, these workloads must work with massive data structures accessed in array format and with sizes ranging from tens of GBs to tens of TBs today and are expected to proliferate in the foreseeable future. However, the maximum memory capacity available in these accelerators, as of 2022, is only 128GB and remains significantly below the emerging workloads memory requirements. Moreover, in these workloads, data lookups are increasingly becoming on-demand, data-dependent and sparse, making it difficult to determine which part of the data is needed when. Intuitively, the key to efficiently analyzing a massive data set in these workloads is strategically touching as little data as possible for each application-level query. However, as we discuss in the next chapter, the traditional CPU-centric model where the CPU performs data orchestration severely limits the performance of existing systems.

## Chapter 4

# Issues with Current State-of-the-Art and Motivation

To address the memory capacity wall, application developers and system designers use fast NVMe solid-state-drives (SSDs) and rely on the application and operation system (OS) running on the CPU to orchestrate the data movement between the GPUs, CPU memory, and SSDs while supporting standard abstractions such as memory-mapped files [14–18,20,22–24,26,27,31]. In this chapter, we present three approaches, namely proactive tiling (§ 4.1), reactive page faults (§ 4.2) and leveraging pooled memory (§ 4.3), used by the state-of-the art CPU-centric systems to alleviate memory capacity limitation and also motivate the BaM design.

### 4.1 I/O Amplification Problem With Proactive Tiling

Proactive tiling is a CPU-centric solution that requires the programmer to explicitly decompose and partition the data into tiles that fit into the GPU memory. The CPU application code orchestrates data movement between the storage and the GPU memory to *proactively* preload tiles into GPU memory. It also launches compute kernels for each tile and combines the results from processing the individual tiles. Proactive tiling is effective for traditional GPU applications with predefined, regular, and dense access patterns, but it is difficult for emerging applications with dynamic, data-dependent, irregular access patterns, like data analytics. The developers are forced to use coarsegrain tiles due to the synchronization and CPU orchestration's execution time overhead, which exacerbates I/O amplification.

Consider running data analytics queries on the NYC taxi dataset described in §3.3. For executing Q1, the programmer must process the data in smaller row groups that fit in GPU memory as explained in §4.1 as the dataset has almost 1.7 billion rows and exceeds the GPU memory limit. The program-

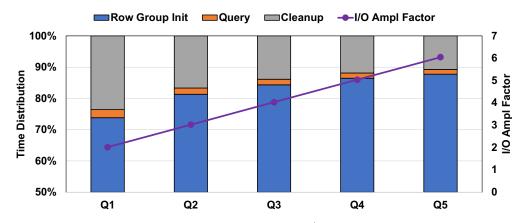

Figure 4.1: Execution time breakdown and I/O amplification in GPU accelerated data analytics application with the proactive tiling used in the state-of-the-art RAPIDS [6] system.

mer's responsibility can be described in three steps: (1) find and load each row group (i.e., tile) into the GPU memory, (2) perform the query on the GPU over the row group, and (3) aggregate results across row groups. During query computation over the row group, the trip distance column of the row group is scanned, and for trips that meet the criteria with a trip distance greater than 30miles, the amount value of the corresponding total amount array element must be aggregated. Assuming all data is present in the host OS page cache (or host DRAM-only), Figure 4.1 displays the profiling result for running the Q1 query on the cutting-edge GPU-accelerated data analytics platform, NVIDIA RAPIDS framework. Even without storage access, the CPU code to initialize the row group, which entails finding, allocating memory for, and loading each row group of the columnar metric arrays into GPU memory, accounts for more than 73% and the CPU code to clean up the row group account for up to 23% of the end-to-end application time, reflecting the high driver and synchronization overhead.

Furthermore, since accesses to the total amount column are dependent on values in the trip distance column, the CPU cannot determine which total amount rows are required without explicit synchronization with the GPU. To address this, the state-of-the-art GPU accelerated data analytics framework, RAPIDS [6], trades off the cost of serialization with the storage bandwidth and fetches all rows of both columns from storage or host memory to GPU. As only 511K trips have their trip distance greater than 30miles, and thus only 0.03% of the second column will be used<sup>1</sup>. As a result, the proactive tiling approach results in  $2.02 \times \text{ I/O}$  amplification for this query.

Figure 4.1 shows the I/O amplification in the RAPIDs framework for the rest of the queries described in §3.3. The I/O amplification is computed as the ratio of bytes RAPIDS reads into the GPU over the minimum bytes needed to execute each query. Furthermore, the CPU-centric approach results in gross I/O amplification with additional data-dependent metrics added on top of Q1. This is mainly because the CPU cannot determine which parts of each data-dependent column are required and ends up moving entire columns to the GPU memory. Hence, I/O amplification suffered by the CPU-centric model linearly scales to over  $6 \times$  as the number of data-dependent metrics increased, as shown in Figure 4.1. The fine-grained, on-demand storage access capability in BaM mitigates such I/O amplification problems.

#### 4.2 Software Overhead With Reactive Page-faults

Some applications, such as graph traversal, can not cleanly partition their datasets and thus prefer keeping whole data structures in the GPU's address space [5]. For example, assume that a graph is represented in the popular compressed sparse row (CSR) format, where the neighbor-lists of all nodes are concatenated into one large edge-list array. An array of offsets accompanies the edge-list, where the value at index i specifies the starting offset for the neighbor-list of node i in the large edge-list. Since any node, and its corresponding neighbor-list, can be visited while traversing a graph, traversal algorithms prefer to keep the entire edge-list in the GPU's address space [5].

Starting with the NVIDIA Pascal architecture, GPU drivers and programming model allow the GPU threads to implicitly access large virtual memory objects that may partly reside in the host memory using Unified Virtual Memory (UVM) abstraction [28]. Prior work shows that the UVM driver can be extended to interface with the file system layer to access a memorymapped file [25]. This enables a GPU to generate a page fault for data, not in GPU memory which the UVM driver *reactively* services by making I/O request(s) for the requested pages on storage.

However, this the approach introduces significant software overhead in

<sup>&</sup>lt;sup>1</sup>It is impossible to avoid transferring trip distance column.

Figure 4.2: UVM page fault overhead for BFS graph traversal application across different datasets.

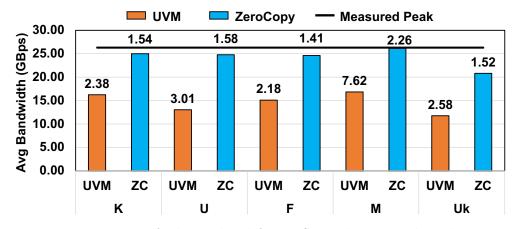

page fault handling mechanisms when the accessed data is missing from GPU memory. Figure 4.2 shows the measured host-memory-to-GPU-memory data transfer bandwidth for an NVIDIA A100 GPU in a PCIe Gen4 system executing BFS graph traversal on six different datasets (See Table 7.2) where the edgelists are in the UVM address space and initially in the host memory. In these experiments, there is no storage access, and measured data bandwidth is an upper bound of what a page-fault-based approach might potentially achieve.

From Figure 4.2, the average PCIe bandwidth achieved by the UVM page faulting mechanism is  $\sim 14.52$ GBps which is only 55.2% of the measured peak PCIe Gen4 bandwidth, 26.3GBps. Profiling data shows that the UVM fault handler driver on the CPU is 100% utilized, and the maximum UVM page fault handling rate saturates at  $\sim 500$ K IOPs. Such a rate is only half the peak throughput of a consumer-grade SSD like the Samsung 980 pro SSD, as noted in Table 5.3.

With these limitations, even if we integrate the file system layer into the UVM driver and assume no additional overhead, the UVM page fault handling mechanism cannot generate requests at a sufficiently high rate to fully utilize even one consumer-grade SSD for page sizes of 8KB or smaller. Thus the page-fault-based approach is a no-go for the targeted applications.

#### 4.3 Cost Effectiveness With Pooled Memory

Applications can leverage CPU memory or even pool the memory of multiple GPUs to host large data structures. In the graph traversal example, the programmer allocates pinned (or zero-copy) buffers in these memories, loads the edge-list data from storage into the buffers, and maps the buffers into the address space of the GPU(s) executing the computation. The GPU threads can then access these buffers in cache-line granularity, and the GPU provides sufficient memory-level parallelism to saturate the interconnect between the GPU and these memories. Thus, these solutions can out-perform the UVM solution for critical graph traversal applications, as shown in Figure 4.2 and by previous works [5].

However, regardless of which memory, CPU or pooled GPU, is used to host these data structures, this approach suffers from two major pitfalls. First, data must still be loaded from the storage to the memory before any GPU computation can start. Often this initial data loading can be the main performance bottleneck as the dataset sizes are in GBs while the computation kernel requires only a few milliseconds to execute. Later in the evaluation (§ 7.1.1) we shall compare the proposed system with this Target (T) system). Second, hosting the dataset in CPU or pooled GPU memory requires scaling the available memory, by either increasing the CPU DRAM size or the number of GPUs in the system with the dataset size. Either of these two approaches is prohibitively expensive in terms of dollar cost for massive datasets. Moreover, there is a limit to the dataset sizes these systems can scale beyond which it is physically infeasible.

### 4.4 NVIDIA GPUDirect Storage And Challenges

NVIDIA GPUDirect Storage (GDS) [17] and several similar CPU-centric prior work [18, 20, 22, 23, 29, 31, 56–59] propose to enable peer-to-peer direct data transfer using GPUDirect RDMA. For storage access, the driver running on the CPU creates a direct data path for direct memory access (DMA) transfer between GPU and storage and avoids a bounce buffer through the CPU memory. The control plane lies squarely in the CPU in all these prior works. Thus, this is excellent if the application access pattern requires loading a large chunk of data, like in the case of the "proactive tiling approach". But these systems pose several challenges for emerging applications that require fine-grain data-dependent access to small request granularities (512B-16KB).

**Programming model problem:** NVIDIA GDS and other proactivetiling-approach-based systems require the CPU application code (basically, the burden is on the developer) to orchestrate the data movement between the storage and the GPU memory by proactively pre-loading tiles, launching computes kernels for each tile, and hoping it provides good performance. This programming model is excellent for workloads with heavy data re-use within the tile. However, as we studied in this chapter, proactive tiling exhibits significant drawbacks for emerging workloads, including I/O traffic amplification, frequent memory allocation and deallocation, constant interaction between GPU and CPU for synchronization, and, most importantly, a complex programming interface for developers.

**Performance problem:** Our microbenchmark study using NVIDIA GDS on an NVIDIA DGX system using single NVMe SSD, shows the NVIDIA GDS can saturate the storage bandwidth when the block size is above 64KB for random access read microbenchmark. However, for accesses at 4KB or lower, the random access read bandwidth is less than 500MBps, far lower than the storage capabilities. These bandwidth numbers are insufficient for providing performance benefits for the emerging workloads.

## 4.5 Little's Law: Leveraging Parallelism To Amortize Storage Access Overhead

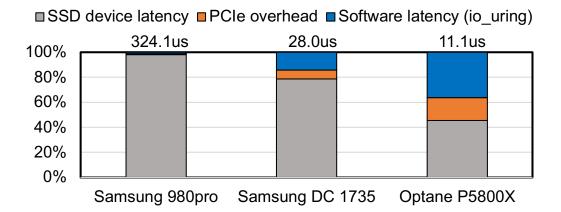

Modern storage devices like SSDs provide very high performance, and their performance is growing yearly. Latest SSDs like Intel P5800X [60] can provide  $10\mu$ s latency and maintain more than 1M IOPs for random 4KB accesses. As the storage device latency is reduced due to technological advancements like Optane or Z-NAND media, the software overhead is becoming a significant fraction of overall I/O access latency. Figure 4.3 shows the latency breakdown of an I/O request from a highly optimized CPU software stack, io\_uring, to three NVMe SSDs: a high-end consumer grade SSD (Samsung 980 Pro) and two high-end ultra low latency data-center grade SSDs (Samsung DC 1735 and Intel Optane P5800X). As device latency decreases, the software

Figure 4.3: Latency breakdown of accessing the storage from CPU at 4KB using io\_uring.

overhead becomes a significant fraction, up to 36.4%, of the total storage access latency.

To address this shift, emerging storage systems allow applications to make direct user-level I/O accesses to storage [61–69]. The storage system allocates user-level queue pairs, akin to NVMe I/O submission (SQ) and completion (CQ) queues, which the application threads can use to enqueue requests and poll for their completion. Using queues to communicate with storage systems forgoes the userspace to kernel crossing of traditional file system access system calls. Instead, isolation and other file system properties are provided through trusted services running as trusted user-level processes, kernel threads, or even storage system firmware running on the storage server/controller [61, 62, 66, 69].

In such systems, the parallelism required to tolerate access latency and achieve full throughput of the device is fundamentally governed by Little's Law:  $T \times L = Q_d$ , where T is the target throughput, L is the average latency, and  $Q_d$  is the minimal queue depth required at any given point in time to sustain the throughput. If we want to achieve the full potential of the critical resource, i.e., PCIe ×16 Gen4 connection providing ~26GBps of bandwidth, then T is 26GBps/512B = 51M/sec and 26GBps/4KB =6.35M/sec for 512B and 4KB access granularities, respectively. The average latency, L, depends on the SSD devices used, and it is  $11\mu$ s and  $324\mu$ s for the Intel Optane and Samsung 980pro SSDs, respectively. From Little's Law, to sustain a desired 51M accesses of 512B each, the system needs to accommodate a queue depth of  $51M/s \times 11\mu s = 561$  requests (70 requests for 4KB) for Optane SSDs. For the Samsung 980pro SSDs, the required  $Q_d$  for sustaining the same target throughput is  $51M \times 324\mu s = 16,524$  (2057 for 4KB). Note that  $Q_d$  can be spread across multiple physical device queues. To sustain T over a computation phase, there needs to be a substantially higher number of concurrently serviceable access requests than  $Q_d$  over time.

GPUs provide not only the hardware features needed to hide such latencies, e.g., a massive number of threads and hardware scheduling but also the programming interface, e.g., CUDA, enabling applications to easily express massive parallelism and the high number of concurrently serviceable storage access requests. Thus, by exploiting a sufficient amount of parallelism, GPUs can hide the application storage access latency.

#### 4.6 Summary

We discussed existing three approaches, namely proactive tiling (§ 4.1), reactive page faults (§ 4.2) and leveraging pooled memory (§ 4.3), used by the state-of-the-art CPU-centric systems to alleviate memory capacity limitation. We showed the limitations of current state-of-the-art systems like NVIDIA GDS [17] and discussed why enabling direct access from GPUs can amortize the storage access overhead. In the next chapter, we discuss how BaM addresses the memory capacity problem by enabling fine-grain high-throughput direct access to storage.

# Chapter 5

# BaM: Enabling Fine-grain High Throughput GPU-Orchestrated Access to Storage

### 5.1 BaM Vision And Design Goals

BaM addresses the insufficient GPU memory capacity problem by effectively increasing the memory capacity to terabyte-scale with the storage and uses high-bandwidth memory (HBM) as a software-managed cache. BaM proposes an accelerator-centric computing model in which threads in GPU can access data where it is stored, be it memory or storage, without relying on the CPU or the operating system (OS) to orchestrate the data movement. Using high-level abstractions like arrays, BaM enables accelerators to make on-demand, high-throughput access to storage. BaM uses storage as memory, and this enables BaM to scale to hundreds of TBs of memory capacity at a reasonable cost and yet be performant across applications.

BaM's userspace software-managed cache enables application threads to find data in parallel without relying on the traditional centralized authorities like the page-fault handlers in the operating system. BaM distributes and parallelizes the cache management across GPU threads and takes full advantage of the modern GPU's massive parallelism, memory bandwidth, and high atomic operation throughput. This makes BaM's cache scalable to thousands of threads and provides high throughput for applications when data resides in the GPU memory.

Unlike traditional memory mapped objects, BaM does not allocate a range of addresses within the virtual address space of a process for a BaM data object. Rather, BaM assigns an ID to each BaM data object and allows applications to access its elements using an offset which alleviates the problem of requiring a consecutive range of virtual addresses to host a memory-mapped storage object in a process' available virtual address space. For example, when two or more processes share a BaM data object, as long as they use

Figure 5.1: High level overview of BaM software stack.

the same BaM object ID, the BaM caches can manage the coherence between the BaM caches of these processes without the need to find a common range of locations in all the virtual address spaces of these processes<sup>1</sup>.

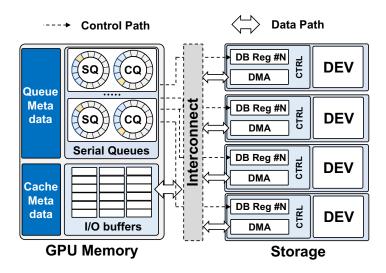

While the CPU-centric storage access orchestration suffers from a low degree of CPU thread-level parallelism available to the OS page-fault handlers and device drivers, there is currently a lack of mechanisms for orchestrating storage accesses from GPUs. To address this issue, BaM provides a user-level library of highly concurrent submission/completion queues in GPU memory that enables GPU threads whose on-demand accesses miss from the software cache to make storage accesses in a high-throughput manner. This user-level approach removes the page fault handling bottleneck, incurs little software overhead for each storage access, and supports a high degree of thread-level parallelism.

Figure 5.1 summarizes the overall block diagram of BaM. BaM provisions storage I/O queues and buffers in the GPU memory and maps the storage doorbell registers to the CUDA address space (see §5.3). As storage devices have relatively low bandwidth and GPUs have limited memory capacity, BaM uses a high-throughput cache for optimal usage of these resources for applications (see §5.3.2). Also, since the existing GPU kernels generally do not expect to make storage accesses, BaM must provide high-level abstractions that hide BaM's complexity and make it easy for the programmer to inte-

<sup>&</sup>lt;sup>1</sup>Supporting multiple data objects and sharing data objects across processes is under active development, goes beyond the scope of the thesis, and is part of our future work.

Figure 5.2: Life of a thread in BaM.

grate BaM into their GPU kernels (see §5.3.3). Lastly, emerging applications require high memory capacity for large data structures today. We show that it is possible to build a cost-effective prototype BaM system using existing off-the-shelf hardware components (see §5.3.4).

#### 5.2 BaM System Overview

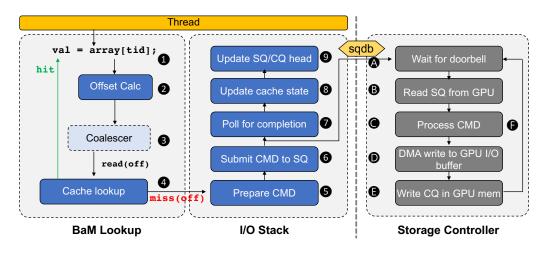

Figure 5.2 shows a programmer's view of the BaM system architecture. BaM presents bam::array high-level programming abstraction for easy integration with the existing application. An application can call BaM APIs to initialize the bam::array with data backed by storage, akin to mmap'ing a file.

Each GPU thread uses the abstraction to determine the cache-line offset (or virtual byte range) for the data being accessed 1. The thread then uses the offset 2 to probe the BaM software cache 4 in GPU memory. The abstraction also has warp-level coalescer 3 that can detect if multiple threads in warp access the same cache-line. If so, only one of these threads requires probing the cache on behalf of the rest and thus effectively increases the efficiency of accesses.

The thread can directly access the data in GPU memory if access hits the cache. If the access misses (4), the thread must fetch data from the backing memory. The BaM software cache is designed to optimize the bandwidth utilization to the backing memory in two ways: (1) by eliminating redundant simultaneous requests to the backing memory and (2) by allowing users to

have fine-grain control of cache residency for their data.

If the storage system or device is backing the data, the GPU thread enters the BaM I/O stack to prepare a storage I/O request (5), enqueues it to a submission queue (6), and then waits for the storage controller to post the corresponding completion entry (7). BaM exploits the massive thread-level parallelism offered by the GPU to amortize long latency accesses to the SSD and enables low-latency batching of multiple submission/completion queue entries to minimize the cost of expensive doorbell register updates in the storage protocol. On receiving the doorbell update (A), the storage controller fetches the corresponding submission queue entries (B) and processes the command (C) to transfer the data between SSD and the GPU memory (D). At the end of the transfer, the storage controller posts a completion entry in the CQ (E). After the completion entry is posted, the thread updates the cache state (8) for the key, updates the SQ/CQ state (9), and then can access the fetched data in GPU memory.

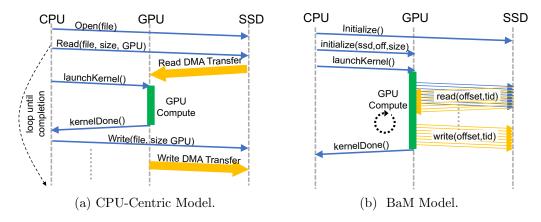

#### 5.2.1 Comparison With The CPU-Centric Design

A comparison between the BaM approach and the traditional CPU-centric model, as shown in Figure 5.3a, highlights three main advantages of BaM. The first is proactive tiling; as the CPU manages the storage data transfer and GPU compute, it copies data between the storage and GPU memory, launching compute kernels multiple times to cover a large dataset. This is done with driver code with very limited thread-level parallelism and thus limited performance. Furthermore, each kernel launch and termination incurs costly synchronization between the CPU and the GPU. Since BaM allows GPU threads to compute and fetch data from storage, as shown in Figure 5.3b, the GPU doesn't need to synchronize with the CPU as frequently and can do more work in a single GPU kernel. Furthermore, the storage access latency of some threads can also be overlapped with the compute of other threads, thus improving the overall performance.

Second, because the compute is offloaded to the GPU and the data orchestration is managed by the CPU in the proactive tiling, it is difficult for the CPU to determine which parts of the data are needed and when they are needed; thus, it fetches many unneeded bytes. With BaM, a GPU thread

Figure 5.3: Comparison between the traditional CPU-centric and BaM computation model is shown in (a) and (b). BaM enables GPU threads to directly access storage enabling compute and I/O overlap at fine-grain granularity.

fetches the specific data it needs only when required, reducing the I/O amplification overheads that the proactive tiling approach suffers.

Third, in the proactive tiling, programmers expend effort to partition the application's data and overlap compute with data transfers to hide storage access latency. BaM enables the programmer to naturally harness GPU thread parallelism across large datasets to hide the storage access latency.

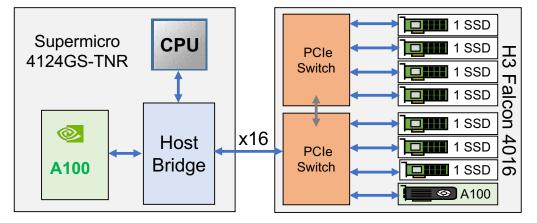

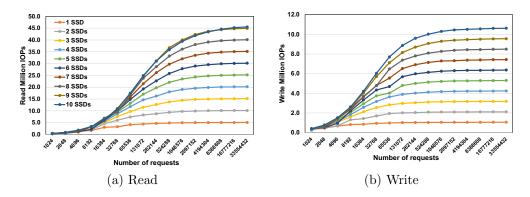

# 5.3 The Design Of A BaM Prototype

We discussed the design philosophy and high-level working of BaM system. We use off-the-shelf hardware, including NVIDIA GPUs and arrays of NVMe SSDs, to construct a BaM prototype. We show the benefits of allowing GPUs to directly access storage with enough random access bandwidth to take full advantage of a GPU's PCIe Gen4 x16 link. Once this level of data access bandwidth is achieved, a storage-based solution is as good as a host memory accessed through PCIe in terms of performance but significantly cheaper. For simplicity, we describe the prototype assuming bare-metal, direct access to the NVMe SSDs.

### 5.3.1 Enable Direct NVMe Access From GPU Threads

For simplicity, we will use the NVMe SSD controllers as a simple example of storage controllers to explain the key features of the BaM. To enable GPU threads to access data on storage devices directly, we need to: 1) move the storage queues, i.e., NVMe queues and I/O buffers from CPU memory to GPU memory and 2) enable GPU threads to write to the queue doorbell registers in the NVMe SSD's BAR space. To this end, we create a custom Linux driver that creates a character device per NVMe SSD in the system, like the one by SmartIO [70]. Applications use BaM APIs to open the character device for each SSD they wish to use.

In the custom Linux driver, BaM leverages GPUDirect RDMA features discussed in § 2.2 to pin and map NVMe queues and I/O buffers in the GPU memory. BaM uses the nvidia\_p2p\_get\_pages kernel API to pin the pages of NVMe queues, and I/O buffers pre-allocated in the GPU memory and then maps these pages for DMA access from another third-party PCIe device, like NVMe SSDs, using nvidia\_p2p\_map\_pages kernel API. This enables the SSD to perform peer-to-peer data reads and writes to the GPU memory.

We leverage GPUDirect Async, discussed in § 2.2, to memory-map the NVMe SSD doorbells to the CUDA address space so that the GPU threads can ring the doorbells on demand. We use cudaHostRegister API with the cudaHostRegisterIoMemory flag to memory-map the SSD's BAR space into the application's address space. Using cudaHostGetDevicePointer, the application gets the virtual address that the GPU threads can use to ring the NVMe SSD doorbell registers. We note that other storage systems can be enabled similarly.

Next, we need to implement the storage I/O queues in the GPU memory and allow thousands of threads to synchronize and submit I/O requests to the device. BaM leverages the GPU's massive thread-level parallelism and fast hardware scheduling to maintain the queue depths needed to hide storage access latency and saturate the storage throughput. However, ringing doorbells, say after enqueueing commands or cleaning up SQ entries, in the existing storage I/O protocols require serialization. When a thread rings a doorbell, say to enqueue an I/O request, it must make sure that no other thread is writing to the same register and that the value it is writing is valid and is a newer value than any value written to that register before. A naive solution for the serialization problem would be to acquire a lock before enqueueing a command to the submission queue and ring the doorbell. However, with the thousands of parallel threads on the GPU, such a design can lead to high latency and, more importantly, low throughput, as all I/O requests can get serialized. To address this, BaM exploits the CUDA memory consistency model (Volta architecture or later) and implements fine-grain memory synchronization enabling many threads to enqueue I/O requests in the SQ, poll the CQ, or mark queue entries for cleanup in parallel and without any locks. Threads only enter critical sections for moving the SQ's tail and CQ's head and ringing the doorbell. Since threads that enter a critical section move the head or tail as far as possible, most threads that make an I/O request never need to enter any critical section. This enables BaM to submit many concurrent I/O requests to the SSDs.

## 5.3.2 BaM's Software Cache

The BaM software cache is designed to enable optimal use of the limited GPU memory and off-GPU bandwidth. Traditional cache design used a centralized cache controller to manage cache entries and data buffers. Instead, BaM focuses on using each GPU thread as a software cache controller and uses atomic operations on the global state to manage cache metadata and data buffers. This enables BaM's cache to scale to thousands of threads and provides very high throughput for applications when data resides in the GPU memory.

Furthermore, traditional kernel-mode memory management (allocation and translation) implementations must support diverse, legacy application/hardware needs. As a result, they contain large critical sections that limit the effectiveness of multi-threaded implementations. BaM addresses this bottleneck by pre-allocating all the virtual and physical memory required for the software cache when starting each application. This approach allows the BaM software cache management to reduce critical sections, only requiring a lock when inserting or evicting a cache-line, which helps the BaM cache to support many more concurrent accesses.

BaM implements a reference counter based write-back cache. Each cacheline in the BaM cache has information about its mapping and it's current cache state. Each cache-line can be in either (a) Invalid (I), (b) Valid (V), and (c) Valid Dirty (D) state. BaM manages the cache state of each cache-line using atomic operations. BaM encodes the state and reference counts in a 32-bit unsigned word where three most-significant bits represents the cache states and the least-significant 29 bits of the word represent the reference count. This encoding helps manage the state and reference count using one fused atomic operation. For instance, a thread can just execute cur\_state = state[i].fetch\_add(1, acquire) to increment both the cache-line reference count by one and read the cache-line's state.

When a thread probes the cache with an offset, it directly checks the corresponding cache-line's state with the fetch\_add atomic operation and increments the reference count. If the cache-line is invalid, the thread tries to set the cache state to Busy state to lock the cache-line using fetch\_or operation. This locking prevents multiple requests to the backing memory for the same cache-line, exploiting spatial locality in the data and minimizing the number of requests to the backing memory. If the returned state from the fetch\_or operation has the Busy bit unset, then the thread was successful in moving the state to Busy, and it can proceed with finding a victim to evict and requesting the data from the backing memory. If the returned state has the Busy bit set, then the thread must wait for the cache-line to become not Busy. After the cache-line is brought into the cache, the thread obtained the lock must move the cache state from Busy to Valid. This can be done using a fetch\_xor operation. Once the cache state is in the Valid state, the thread can use the data in the cache-line. When the thread is done using the cache-line, its reference count is decremented.

When the thread probes the cache, it increments the reference count and checks if the state is in the Valid state. If the state is Valid, then the thread can directly use the data from the cache-line. Reference counting helps to determine if threads expect the data to be available in the cache and ensure no other thread evicts the cache-line until the thread has copied the data to its registers. This is important, especially working with concurrent cache accesses, as there is no guarantee in ordering from the hardware when the operations will get scheduled. Thus, it is crucial to ensure that when the thread accesses the data, it gets the correct data. The use of reference count provides such guarantees for the thread accessing the data by providing some notion of pinning of cache-line until the thread copies the data into its registers. Reference count increment occurs when the higher level API such as bam::array<T> performs a probe operation using cache->coalesced\_acquire() (see Listing 5.1 line 8) to read the data into its thread's register. The reference count is decremented when the thread successfully calls the cache->coalesced\_release() operation ((see Listing 5.1 line 10). If the thread is writing to the cache-line, it will also set the cache-line's dirty bit.

The BaM cache uses a clock replacement algorithm proposed by F.J. Corbató [71] to enable concurrent evictions at different cache-lines and avoid contentions among concurrent evictions. The cache has a global counter that gets incremented when a thread needs to find a cache slot. The returned value of the counter tells the thread which cache slot to attempt to use. As BaM implements a concurrent cache, the cache state can have both the Valid and Busy bit set simultaneously with a non-zero reference count; it is essential to ensure the suitable victim is evicted out. For instance, when a thread probes the cache to find a slot to evict, the cache-line state can be Valid with a reference count equal to zero. When the thread tries to evict this cache-line, it needs to ensure the reference count does not change until the cache state transitions to the Busy state. This can happen as another thread in the GPU could increment the reference count observing the Valid bit in the state. If the evicting thread finds the victim to have a non-zero reference count or change in reference count or has the Busy bit set by another thread, the evicting thread will abort, resetting the Busy bit if it was the one that set it and find another victim by incrementing the counter and attempt to take the next cache slot.

## 5.3.3 BaM Abstractions And Software APIs

BaM's software stack provides the programmer an array-based high-level API (bam::array<T>), consistent with array interfaces defined in modern programming languages (e.g. C++, Python, or Rust). As GPU kernels operate on such arrays (see § 3.4), BaM's abstraction minimizes the programmer's effort to adapt their kernels. Listing 5.2 shows a random access GPU kernel code representative of graph analytics workload. To port the kernel to use BaM, only the data structures that require to be mapped with BaM (i.e.,

```

1

template <typename T>

struct array {

\mathbf{2}

3

. . .

4

T operator[](size_t i){

5

size_t clid = get_cl_id(i);

6

size_t cl_sub_idx = i % (cache->cl_size/sizeof(T));

7

8

T* cl_addr = cache->coalesced_acquire(cl_id);

9

T val = cl_addr[cl_sub_idx];

cache->coalesced_release(cl_id);

10

11

return val;

12

}

13

14

private:

15

BamCache* cache;

16

. . .

17|

```

Listing 5.1: High level overview of bam::array<T> abstraction design with warp coalescing.

```

1 __global__ void kernel(float *data,

2 size_t n, float *out, unsigned* randidx) {

3 size_t tid = blockIdx.x * blockDim.x + threadId.x;

4 for(; tid < n; tid += (blockIdx.x * blockDim.x))

5 *output += data[randidx[tid]];

6 };

```

Listing 5.2: Random access GPU kernel code representative of graph analytics application access pattern.

```

1 __global__ void kernel(bam::array<float> data,

2 size_t n, bam::arrray<float> out, unsigned* randidx) {

3 bam::array_ref ref(&data);

4 size_t tid = blockIdx.x * blockDim.x + threadId.x;

5 for(; tid < n; tid += (blockIdx.x * blockDim.x))

6 *output += ref[randidx[tid]];

7 };

```

Listing 5.3: BaM GPU kernel code with bam::array<T> abstraction for random access. With BaM's bam::array<T> abstraction, base GPU code requires minimal changes to the baseline codebase to support accessing data from storage.

data and out) need to be changed to bam::array<T> type, and the rest of the kernel can remain intact, as shown in Listing 5.3. The bam::array<T>'s

overloaded subscript operator enables the accessing threads to coalesce their accesses, query the cache, makes I/O requests on misses, and return the appropriate element of type T to the calling function. In contrast, the proactive tiling CPU-centric model requires complete, non-trivial application rewrites to decompose the compute and data transfers into tiles that fit within the limited GPU memory.

BaM initialization requires allocating a few internal data structures that are reused during the application's lifetime. These data structures are used to instantiate storage devices, allocate memory for cache and I/O buffers, and map data ranges and layouts. Initialization can happen implicitly through a library construction if no customization is needed. Otherwise, the application specializes in the memory through template parameters to BaM 's initialization call, a standard practice in C++ libraries. BaM also provides four memory implementations for bam::array<T>: (1) storage with BaM's cache (default), (2) pinned CPU memory with BaM's cache, (3) pinned CPU, and (4) GPU memory. However, in most cases, specialization and fine-tuning are unnecessary, as shown later in § 7 where only BaM 's default parameters are used.

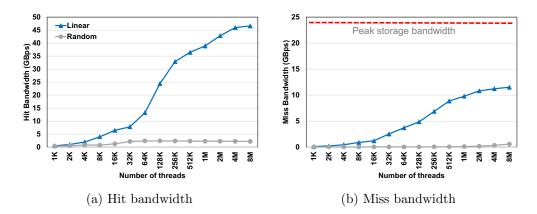

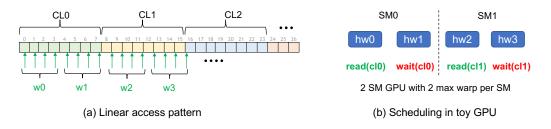

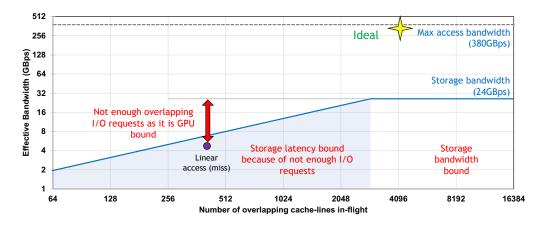

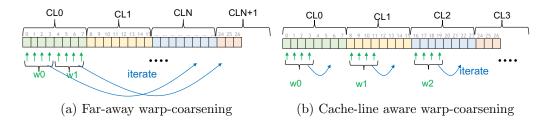

The bam::array<T> abstraction implements two additional optimizations: warp coalescing and cache-line reference reuse to improve the performance further when accessing the data from the cache. Warp coalescing improves the spatial reuse of cache-line metadata while the cache-line reference reuse exploits the temporal reuse of the cache-line metadata. More in depth design and implementation discussions on of these optimization can be found in [72].