# TECHNIQUES FOR INTEGRATED ENERGY-EFFICIENT POWER CONVERSION

#### BY

### NILANJAN PAL

### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois Urbana-Champaign, 2021

Urbana, Illinois

#### Doctoral Committee:

Professor Pavan Kumar Hanumolu, Chair Associate Professor Robert Pilawa-Podgurski

Professor Jose E Schutt-Aine

Assistant Professor Arijit Banerjee

Assistant Professor Jin Zhou

### ABSTRACT

Power converters are a fundamental part of any system that seek to transfer electrical energy from one voltage domain to another. Traditionally, the power converter required bulky off-chip power switches to maintain acceptable efficiency which resulted in them occupying a significant portion of the total system volume. As these systems evolved to reduce in volume the corresponding power converters needed to adapt by improving both power density and efficiency. This eventually led to the integration of power switches along with the control circuitry on a single die. This integration presented unique opportunities and challenges from a power converter perspective which has resulted in a renewed focus on integrated power converters.

The various DC-DC power converter topologies can be broadly categorised into two classes: switched-inductor and switched-capacitor types. Generally, the switched-inductor type is more suitable for power levels of the order of a few watts or higher, while the switched-capacitor type is more suited to low-power applications of a few hundred milli-watts. Recently, a third category has emerged: hybrid converters which tries to combine the advantages of both the aforementioned categories. The relatively new type of power converter primarily aims to improve power efficiency by easing the trade-off between switching and conduction loss by enabling the use of better power switches.

In the first technique, a hybrid boost converter architecture for improving the efficiency of LED drivers used in mobile applications, is presented. By cascading a low-switching frequency time-interleaved series-parallel SC-stage with an inductive boost converter, we facilitate lower voltage-rated switches, thus significantly reducing the switching losses. Charge-sharing losses of the SC stage are minimized by soft-charging flying capacitors with the inductor of the boost stage. Fabricated in 180 nm BCD process, the prototype converter generates 30 V output voltage from a Lithium-ion (Li-ion) battery source. It can provide a load current in the range of 0 to 100 mA with an excellent peak

power efficiency of 91.15% at 30 mA, which represents a 3% improvement over the state-of-the-art.

In the second technique, a novel current sensing architecture is explored. A new duty-cycle sensing technique with applications in current sensing for DC-DC power converters is presented. A time-based  $\Delta\Sigma$  ADC with 1-bit delay-DAC accurately measures small changes in the duty-cycle of a PWM waveform. Fabricated in 65 nm general purpose CMOS process, the prototype senses changes in duty-cycle ranging from 4 m up to 20 m with 1% linearity, making it suitable for detecting small load current-dependent changes in the duty-cycle of a regulated DC-DC power converter.

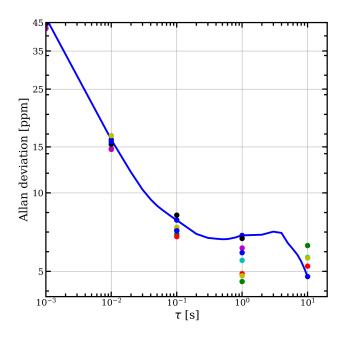

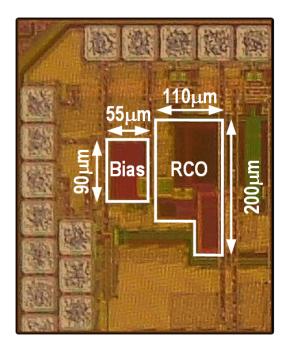

The switching clock of a power converter is an important part of the whole system. It is essential to keep the frequency of this clock fixed under various operating conditions in order to prevent the generation of unwanted harmonics which might interfere with the proper functioning of the whole system. For most low-frequency integrated power converters, an on-chip relaxation oscillator is used. Even though this oscillator architecture is very power efficient, it has large variation in frequency over temperature. A method for improving the temperature stability of RC relaxation oscillators by precisely interpolating between resistors with opposing temperature coefficients is presented. By obviating the need for a large trimming network of switches and resistors, it achieves excellent frequency accuracy across PVT. Fabricated in 65 nm CMOS, the prototype 400 kHz oscillator achieves an inaccuracy of 16 ppm/°C (-40°C to 85°C), 2.5 ppm/mV voltage sensitivity, and 5.6 ppm Allan deviation in one second strides.

To my parents, for their love and support.

### ACKNOWLEDGMENTS

According to Albert Einstein, time is supposed to slow down for people traveling with high velocities measured from an inertial frame of reference. But going to graduate school has taught me that there is a big difference between measured time duration and perceived time duration. For even though the earth is hurtling around the sun at a whopping velocity of about 100,000 km/hr, I clearly remember the day I came to the U.S. for my higher education more than four years ago, as if it were yesterday. This discrepancy is perhaps because graduate school makes you ask yourself so many questions, both work-related and personal, that the brain has no bandwidth left to observe the passage of this large chunk of time. As I struggled with this unending set of questions, not only did I encounter self-doubt, uncertainty and fatigue, but also long-lasting joy and deep satisfaction. And for this I am most thankful to my advisor, Professor Pavan Kumar Hanumolu. I am forever indebted to him for providing me with the opportunity to pursue my studies in this fabulous university (Go Illini!) and in a way which is very different from other groups doing circuit research in the U.S. He has a surprisingly vast reservoir of patience, which, I am sure, came in handy during the numerous times I had reported to him about my chip not starting in the lab or running into a wall with some design problem. He always had a suggestion worth trying, an untapped research question, a paper edit which had a clearer flow and figures which were always better than my multiple miserable attempts. And through him I came to know so many wonderful people who have also helped me immensely through out my graduate studies. I am thankful to Professor Robert Pilawa for being so patient with me during the initial period. He was always happy to answer my questions on basic principles of hybrid DC-DC converter. I am thankful to Professor Arijit Banerjee for his wonderful teaching in ECE464, which helped me a lot. In addition to everything else, Professor Pavan, Pilawa, and Banerjee also agreed to serve on my final exam committee along with Professors Jose Schutt-Aine and Jin Zhou. I am thankful for their critical feedback during the presentation.

I was very fortunate to come across a really smart set of people from Texas Instruments, Inc., from whom I have learned much. I would like to express my gratitude towards William McIntyre, Travis Eichhorn, Adam Fish, Kory McCarthy, Vamsinath Peddireddy, and Venkatesh Burli for making my internship experience a memorable one.

When I first came to the U.S., I had assumed it would be difficult to find friends here as people from a vastly different cultural backgrounds come to study here. But I was pleasantly surprised to make really good friends here. I would like to thank Charlie Zhu for his continuous help and support regarding my work and his friendship through which I discovered the wonderful world of Chinese cuisine over the numerous dinners in various Chinese joints here in Urbana-Champaign. I would like to thank Mostafa Ahmed and Amr Khashaba for their friendship and support throughout my time here, exchanging notes about the culture and politics of Egypt and India. I am grateful to Yongxin Li for inviting me to his lovely star-gazing sessions, to Kyu-Sang Park for helping me innumerable times in the lab with his superior soldering skills, to Tianyu Wang, Ahmed Abdelrahman, Mohamed Badr and Mahmoud Khalil for fun technical and non-technical discussions in CSL422.

And lastly, I would like to express gratitude to my family for maintaining a healthy and sometimes unreasonable belief that no matter what I would make through this and find myself on the other side. Thank you for your unconditional love and support during these uncertain times.

# TABLE OF CONTENTS

| LIST OF TABLES                                                            | ix |

|---------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                           | X  |

| CHAPTER 1 INTRODUCTION                                                    | 1  |

| 1.1 Power converter architecture choices for better efficiency            |    |

| 1.2 Current-sensing for better system efficiency                          |    |

| 1.3 Highly stable clock source for lower harmonic content in              | 0  |

| output voltage in power converters                                        | 4  |

| 1.4 Dissertation organisation                                             |    |

| CHAPTER 2 A 91.15% EFFICIENT 2.3-5 V INPUT                                |    |

| 10-35 V OUTPUT HYBRID BOOST CONVERTER FOR LED-                            |    |

| DRIVER APPLICATIONS                                                       | 7  |

| 2.1 Introduction                                                          | 7  |

| 2.2 LED driver losses                                                     | 10 |

| 2.3 Proposed Architecture                                                 | 12 |

| 2.4 Circuit Implementation                                                |    |

| 2.5 Measurement Results                                                   | 30 |

| 2.6 Conclusion                                                            |    |

| CHAPTER 3 A 1% LINEAR DUTY-CYCLE SENSOR FOR CUR-                          |    |

| RENT SENSING APPLICATIONS IN BUCK CONVERTERS                              | 38 |

| 3.1 Introduction                                                          | 38 |

| 3.2 Duty-cycle as sensing variable                                        |    |

| 3.3 Proposed Architecture                                                 | 44 |

| 3.4 Circuit Implementation                                                | 48 |

| 3.5 Measurement Results                                                   |    |

| 3.6 Conclusion                                                            | 51 |

| CHAPTER 4 A 400 KHZ RC RELAXATION OSCILLATOR WITH                         |    |

| $16 \text{ PPM}/^{O} \text{ C INACCURACY AND } 2.5 \text{ PPM/MV SUPPLY}$ |    |

| SENSITIVITY                                                               | 52 |

| 4.1 Introduction                                                          | 52 |

| 4.2 Proposed Architecture                                                 | 54 |

| 4.3   | Calibr | ation Pro | cedure   |  |  |  |  |  |  |  |  |  |  |   | 58 |

|-------|--------|-----------|----------|--|--|--|--|--|--|--|--|--|--|---|----|

| 4.4   | Circui | t Impleme | entation |  |  |  |  |  |  |  |  |  |  |   | 61 |

| 4.5   | Measu  | rement R  | esults . |  |  |  |  |  |  |  |  |  |  |   | 64 |

| 4.6   | Concl  | usion     |          |  |  |  |  |  |  |  |  |  |  |   | 69 |

| СНАРТ | TER 5  | CONCLU    | JSION    |  |  |  |  |  |  |  |  |  |  | • | 70 |

| REFER | ENCE   | S         |          |  |  |  |  |  |  |  |  |  |  |   | 73 |

# LIST OF TABLES

| 1.1 | Relationship between DCR and dimension for a 10 $\mu$ H inductance from Coilcraft                   | 2  |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.1 | Percentage reduction in losses with respect to conventional inductive boost converter               | 93 |

| 2.2 | Performance summary and comparison to state-of-the-art                                              | 20 |

|     | LED drivers                                                                                         | 34 |

| 4.1 | Performance comparison of proposed temperature compensated oscillator with state-of-the-art designs | 68 |

## LIST OF FIGURES

| 1.1  | vesting applications                                                          | 1  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | Inductive-based (left) and switched-capacitor-based (right)                   | -  |

|      | DC-DC power converter architectures                                           | 3  |

| 1.3  | Different applications for current sensing in power converters.               | 4  |

| 1.4  | Sense-FET-based and filter-based approaches for current                       |    |

|      | sensing in power converters                                                   | 4  |

| 2.1  | Conventional boost converter-based LED driver                                 | 8  |

| 2.2  | LED driver efficiency versus load current for different out-                  |    |

|      | put voltages and fixed $V_{IN} = 3.7 \text{ V.} \dots \dots \dots$            | 9  |

| 2.3  | Transition loss modeling for turn-ON event of low-side switch.                | 11 |

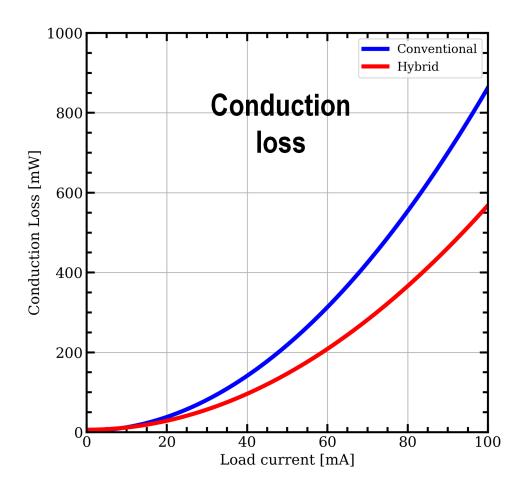

| 2.4  | Electrical switching loss $(P_{transition} + P_{gate})$ and conduction        |    |

|      | loss variation with load current and loss breakdown at 25                     |    |

|      | mA load $(V_{IN} = 3.7 \text{ V}, V_{OUT} = 30 \text{ V})$ for a conventional |    |

|      | inductive-boost power converter                                               | 13 |

| 2.5  | Hybrid boost converter                                                        | 14 |

| 2.6  | Proposed boost converter topology                                             | 14 |

| 2.7  | Relative loss of proposed architecture with SC-stage gain                     |    |

|      | varying from 2 to 4, normalised to corresponding losses in                    |    |

|      | conventional inductive-boost converter                                        | 15 |

| 2.8  | 1:2 switched-capacitor converter with inductor at input                       | 16 |

| 2.9  | Comparison of output impedance of basic hybrid converter                      |    |

|      | with that of the traditional switched-cap converter                           | 17 |

| 2.10 | Time-interleaving of the SC stage to mitigate large output                    |    |

|      | voltage ripple                                                                | 19 |

|      | Efficiency plots of the hybrid and conventional architectures                 | 20 |

|      | Switching loss comparison                                                     | 21 |

|      | Conduction loss comparison                                                    | 22 |

| 2.14 | Simulated power loss breakdown at 25 mA load for the                          |    |

|      | proposed converter                                                            | 23 |

| 2.15 | Phase-by-phase operation and associated waveforms for phase                   | _  |

|      | $\phi_y$                                                                      | 24 |

| 2.16 | Phase-by-phase operation and associated waveforms for phase         |            |

|------|---------------------------------------------------------------------|------------|

|      | $\overline{\phi_y}$                                                 | 25         |

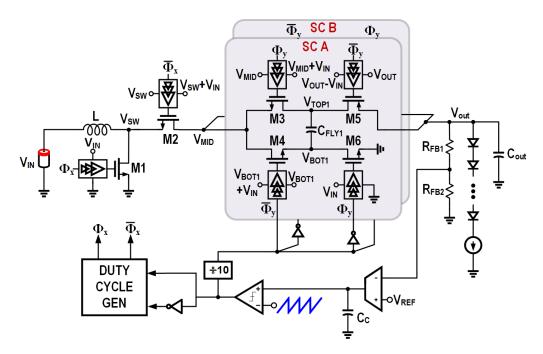

| 2.17 | Full circuit schematic                                              | 26         |

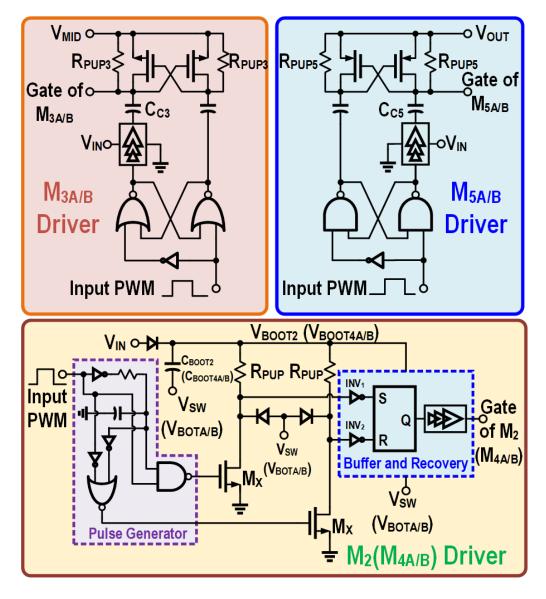

| 2.18 | Gate-driver details for power devices                               | 27         |

| 2.19 | Small-signal model for the proposed architecture in contin-         |            |

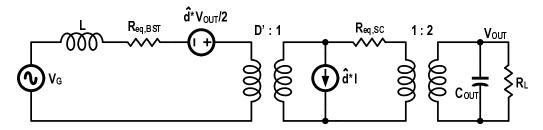

|      | uous conduction mode                                                | 29         |

| 2.20 | Zero-crossing detector circuit used in the discontinuous            |            |

|      | conduction mode                                                     | 29         |

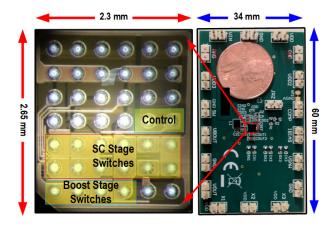

| 2.21 | Die micrograph and evaluation board                                 | 30         |

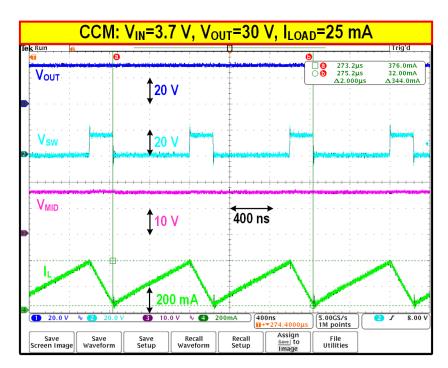

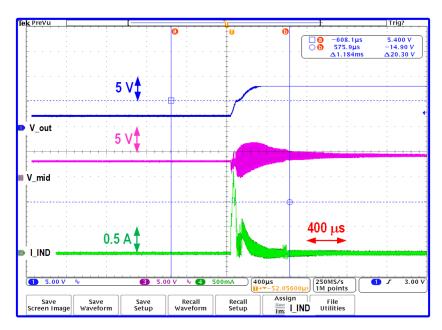

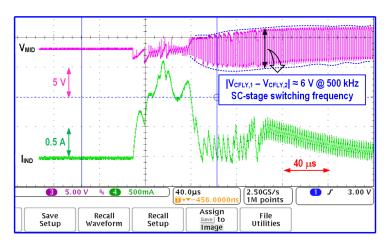

| 2.22 | Steady-state waveforms in CCM                                       | 31         |

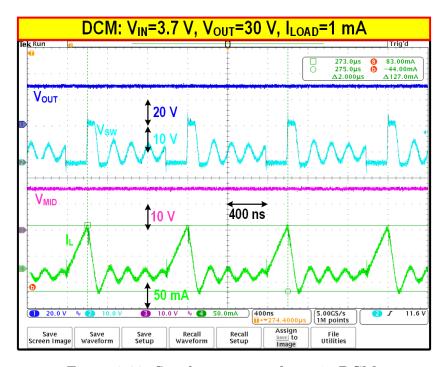

| 2.23 | Steady-state waveforms in DCM                                       | 31         |

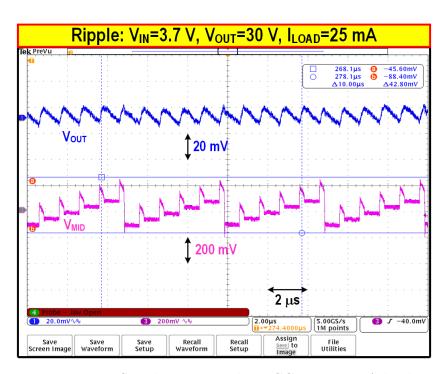

|      | Steady-state ripple in CCM at 25 mA load                            | 32         |

|      | Start-up waveforms for $V_{OUT}$ , $V_{MID}$ and $I_{IND}$          | 32         |

|      | Start-up waveforms for $V_{OUT}$ , $V_{MID}$ and $I_{IND}$ , zoomed | 33         |

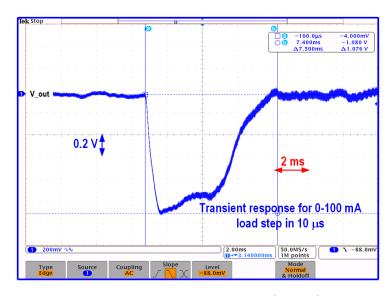

|      | Transient response waveforms for $V_{OUT}$                          | 33         |

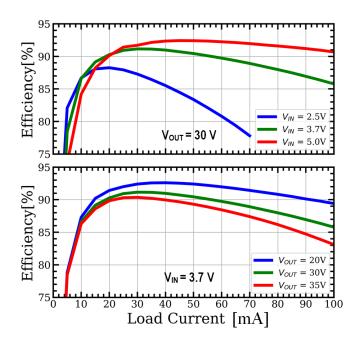

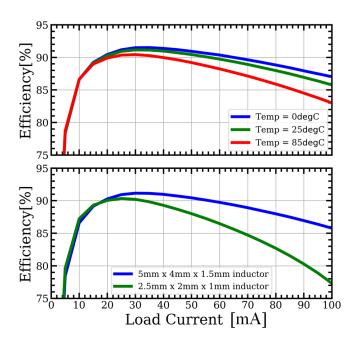

|      | Measured efficiencies at different input and output voltages        | 35         |

| 2.29 | Measured efficiencies with different temperature and exter-         |            |

|      | nal inductance at $V_{IN}$ =3.7 V and $V_{OUT}$ =30 V               | 36         |

| 2.30 | DCM efficiency at loads less than 5 mA                              | 36         |

|      |                                                                     |            |

| 3.1  | Filter-based current sensing                                        | 36         |

| 3.2  | Replica current based current-sensing                               | 36         |

| 3.3  | Average model for buck converter                                    | 41         |

| 3.4  | Load current information in duty-cycle                              | 41         |

| 3.5  | Percentage $R_{OUT}$ variation with load current for a DC-DC        |            |

|      | buck converter                                                      | 42         |

| 3.6  | Comparison of theoretical and simulated duty-cycle varia-           |            |

|      | tion for 1.8 V/1 V $V_{IN}/V_{OUT}$                                 | 43         |

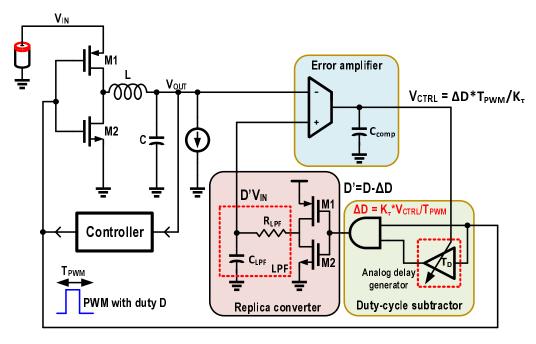

| 3.7  | Conceptual duty-cycle analog loop                                   | 45         |

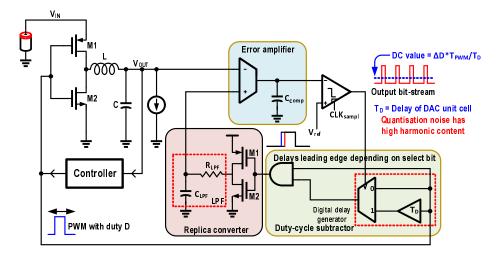

| 3.8  | Digital loop implementation with 1-bit delay-DAC and clocked        |            |

|      | comparator                                                          | 46         |

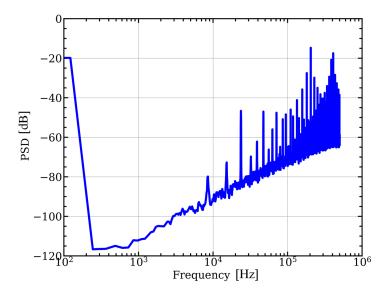

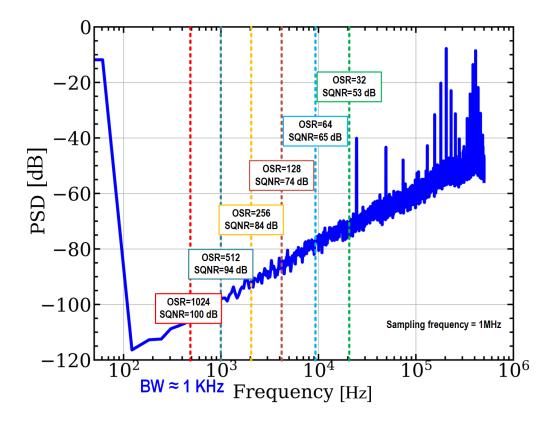

| 3.9  | Power spectral density at the output of the clocked comparator.     | 46         |

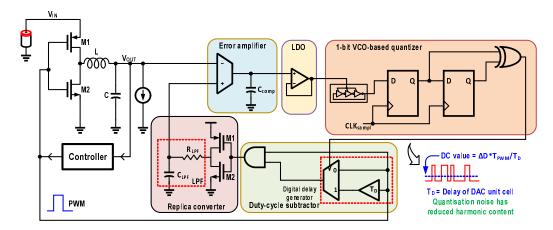

| 3.10 | Digital loop implementation with VCO-based quantiser for            |            |

|      | second-order noise shaping                                          | 47         |

| 3.11 | Power spectral density for a fixed duty-cycle input                 | 48         |

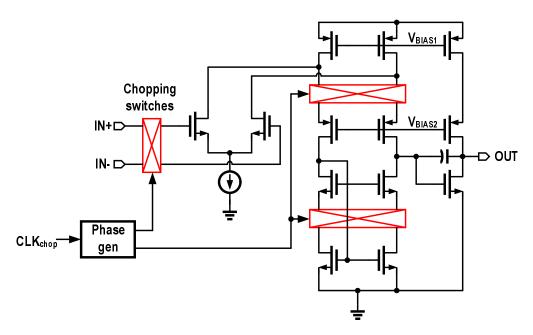

| 3.12 | Error amplifier                                                     | 49         |

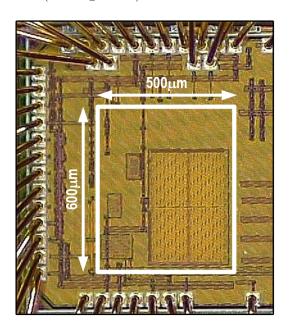

| 3.13 | Die micrograph                                                      | 50         |

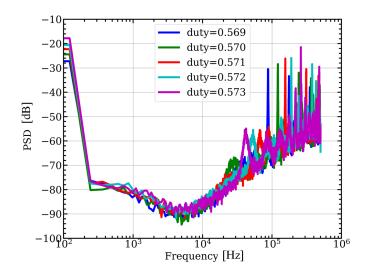

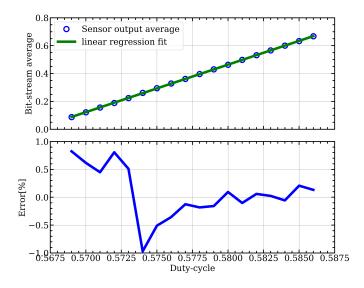

| 3.14 | Prototype output bit-stream PSD                                     | 51         |

| 3.15 | Sensor output with residual error plot after linear regres-         |            |

|      | sion fit                                                            | 51         |

| 1 1  |                                                                     | ۲,         |

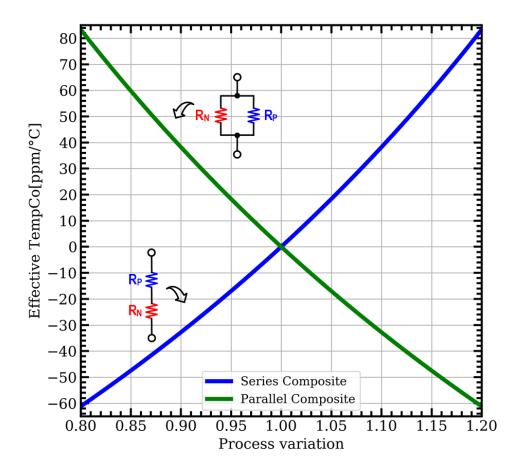

| 4.1  | Temperature coefficient variation under process variation           | 53         |

| 4.2  | Illustration of the proposed RCO temperature compensa-              | <b>-</b> - |

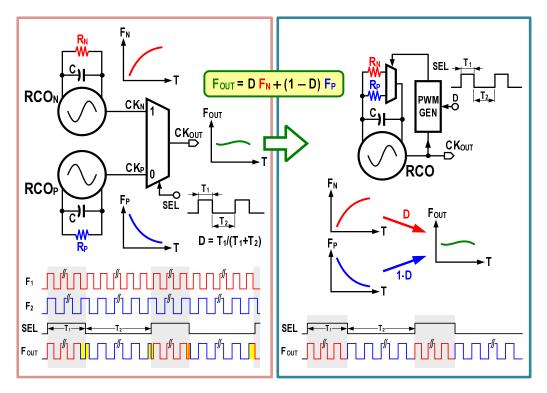

| 4.0  | tion scheme.                                                        | 55         |

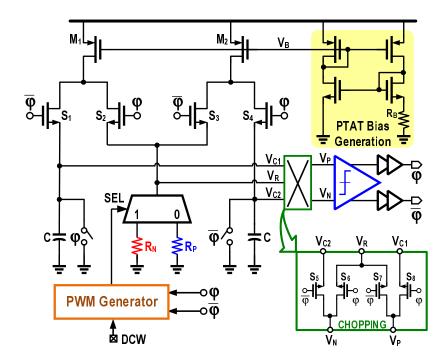

| 4.3  | Proposed RCO architecture                                           | 56         |

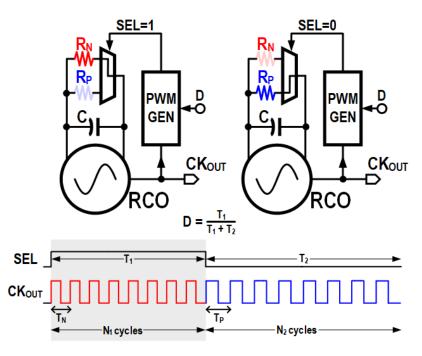

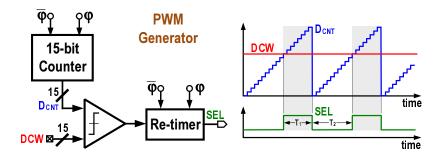

| System operation of proposed architecture                                                             | 57                                                                                      |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

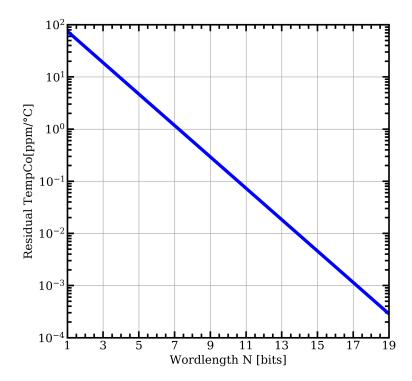

| Residual first order slope error as the word-length of DCW                                            |                                                                                         |

| is increased for $\alpha_N = -300 \text{ ppm/}^{\circ}C$ and $\alpha_P = 150 \text{ ppm/}^{\circ}C$ . | 59                                                                                      |

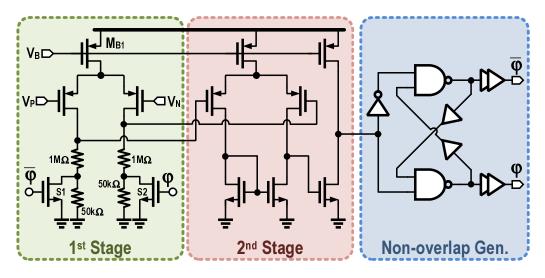

| Comparator schematic                                                                                  | 62                                                                                      |

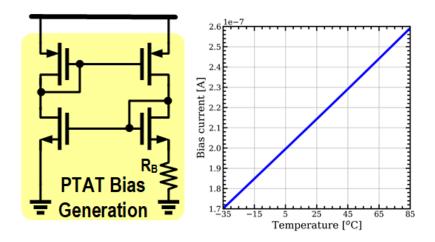

| Constant- $G_m$ biasing                                                                               | 63                                                                                      |

| Counter schematic                                                                                     | 64                                                                                      |

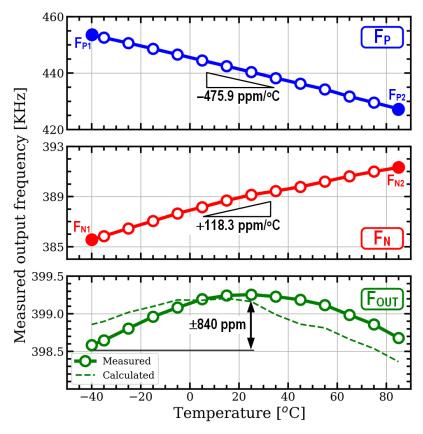

| Measured $F_N$ and $F_P$ across temperature and measured/calculated                                   | d                                                                                       |

| $F_{OUT}$ using optimal duty cycle                                                                    | 65                                                                                      |

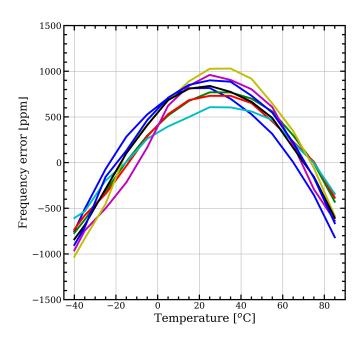

| Measured frequency error versus temperature for eight samples.                                        | 66                                                                                      |

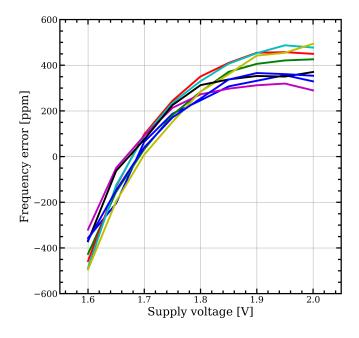

| Measured frequency error versus supply for eight samples                                              | 66                                                                                      |

| Measured Allan deviation versus duration of strides for                                               |                                                                                         |

| eight samples                                                                                         | 67                                                                                      |

| Die micrograph                                                                                        | 67                                                                                      |

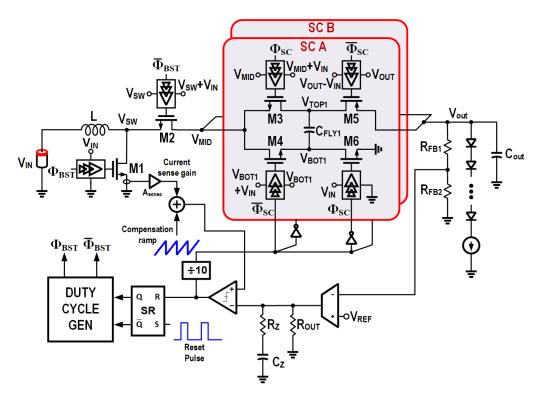

| Current-mode control implementation of the proposed converter.                                        | 71                                                                                      |

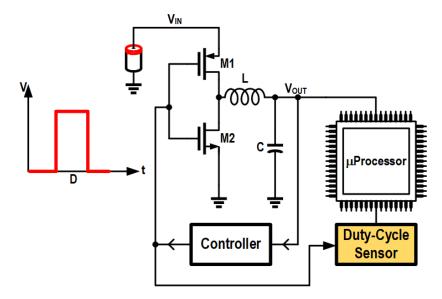

| Duty-cycle sensor with buck converter as a complete cur-                                              |                                                                                         |

| rent sensing solution                                                                                 | 71                                                                                      |

|                                                                                                       | is increased for $\alpha_N=-300$ ppm/°C and $\alpha_P=150$ ppm/°C. Comparator schematic |

### CHAPTER 1

### INTRODUCTION

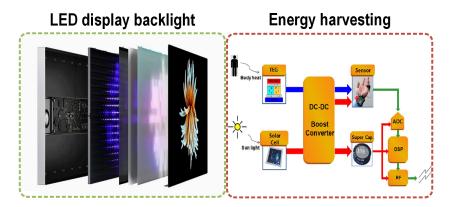

Power converters are integral components of all electronic systems. They are responsible for supplying power to the rest of the system at a preferred voltage level enabling them to perform their functions. For instance, all portable electronic devices have a converter interfacing between the 3 V Liion battery and the various subsystems such as the processor core, memory, display, etc., each requiring a different voltage level. Solar panels have a power converter which provides an interface between the solar cells, that generate a wide range of voltages, and the battery, which stores the power generated by the solar cells at a relatively fixed voltage. Since a significant portion, if not all of the system power, is processed through these converters, high power efficiency of these converters is absolutely essential to maintain an acceptable overall system power efficiency.

Figure 1.1: Boost converter use in LED display drivers and energy harvesting applications.

Table 1.1: Relationship between DCR and dimension for a 10  $\mu H$  inductance from Coilcraft

| DC resistance $[m\Omega]$ | Current rating [A] | $L(mm) \times W(mm) \times H(mm)$ |

|---------------------------|--------------------|-----------------------------------|

| 69.5                      | 3.9                | $4\times4\times3.1$               |

| 200                       | 1.25               | $3.9 \times 3.9 \times 1.8$       |

| 440                       | 0.75               | $2.95 \times 2.95 \times 1.5$     |

| 611                       | 0.66               | $2\times1.9\times1$               |

| 180                       | 0.18               | $1.8 \times 1.12 \times 0.91$     |

# 1.1 Power converter architecture choices for better efficiency

Maintaining high power efficiency in a power converter traditionally meant use of large passive components and switches, as their sizes tended to have an inverse relationship with the losses of the power converter. This is especially true for inductors as shown in Table 1.1. As the size of the inductor reduces the series DC resistance increases steadily. However, relentless progress in semiconductor technology has resulted in diminishing sizes of almost all electronic systems. This has resulted in the constant shrinking of portable electronic systems—so much so that their size and efficiency are limited by the power supply systems they employ. This paved the way for integrated power converters that try to incorporate power-switches and control circuitry onto a single die, yielding highly compact solutions with impressive power density.

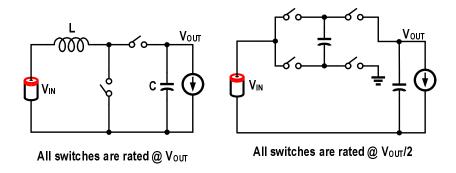

The desired power level decides the type of DC-DC power converter suitable for the application. For applications with power levels up to a few tens of milliwatts, the switched capacitor architecture is most suitable. For high-power applications beyond a few hundred milliwatts, inductive-based architecture is primarily used. Figure 1.2 shows the two types architectures.

Recently, hybrid architectures have been reported as alternatives to both these architectures in various applications [1]. These architectures try to leverage the use of lower-voltage rated switches from the switched-capacitor architecture but avoid high charge-sharing losses by using an inductor in series. The first technique presented in this thesis explores the possibility of a hybrid converter in the context of LED drivers for portable electronic device displays such as mobile and tablet screens. Existing inductive converter

Figure 1.2: Inductive-based (left) and switched-capacitor-based (right) DC-DC power converter architectures.

based techniques dominate the solution space for mobile display LED-drivers. Due to their inherent architectural limitation of using output voltage rated switches, they cannot achieve good efficiency beyond 88% in the best reported LED-drivers at high voltage levels of about 30 V. The hybrid architecture presents an alternative solution with better efficiency at the cost of a slightly increased external component count on the PCB.

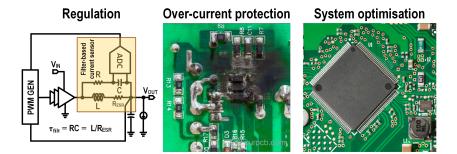

## 1.2 Current-sensing for better system efficiency

Extending battery life is crucial for portable electronic devices such as mobile phones (see Fig. 1.3). Knowledge of the current consumption is often a very useful information in this regard. For instance, embedded software of mobile phones can use this information to optimise its operation. Such optimisations include reducing system-clock frequency, shutting down unnecessary modules not required by the current operation, estimating precisely the remaining battery life of the system [2]. Current-sensing is also used in many regulation schemes for power converters [3] and over-current protection schemes. The accuracy and latency of the current sensing scheme depends on the system requirements. The software/processor based system optimisation application requires more accuracy and can relax on the latency specification. The over-current protection module requires very fast response, hence very low latency, but can be flexible on the accuracy.

In all these applications, the power-converter operating in the system is expected to provide the load-current information. Two principal approaches are used for current sensing in power converters, namely the sense-FET based

Figure 1.3: Different applications for current sensing in power converters.

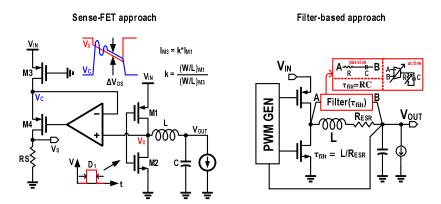

and filter-based approaches, as shown in Fig. 1.4. The accuracy of sense-FET based approach is limited by the settling errors in the amplifier and the mismatch resulting from the large size-ratio between the power-FET and sense-FET. The filter-based approach is mainly used to sense AC current and its use is limited to current-mode control regulation schemes.

Figure 1.4: Sense-FET-based and filter-based approaches for current sensing in power converters.

In view of this, we seek to explore a duty-cycle based current sensing technique, leveraging on the fact that the duty-cycle of a regulated power converter changes with the load current.

# 1.3 Highly stable clock source for lower harmonic content in output voltage in power converters

For most power converters operating at frequencies less than 10 MHz, the clock source is a relaxation oscillator. While these are efficient clock sources

and well-suited for integration, their output frequency has a strong dependence on temperature and process. This is mainly due to the temperature and process dependence of the reference resistor. One way to approach this problem would be make very stable integrated resistors [4]. But, often it is very difficult to procure such a stable resistor in most of the technology nodes in prevalent use today. It is more likely that one can find resistors with opposite temperature coefficients in the popular processes. Simply cascading resistors of opposing temperature trends will not solve the problem as their proportion might vary heavily with process, thus resulting in imperfect cancellation. An array of such resistors with programmable trim settings also won't give good performance as the switches in the trim DACs degrade temperature performance. In view of this, we seek to explore a novel resistor DAC with minimal use of switches such that we can achieve very precise interpolation between the resistors in order to obtain an effectively zerotemperature coefficient resistance without significant degradation from the trimming switches.

### 1.4 Dissertation organisation

The focus of this dissertation is on developing techniques which improve system power efficiency of portable electronic systems by exploring different aspects of the power management module used in such devices. The dissertation is organised as follows:

Chapter 2 describes a new hybrid DC-DC boost converter for LED-driver application in mobile phones. It presents the proposed architecture, illustrating its properties and operating principle. This approach is then compared to the existing approach and the benefits are clearly explained. Measured results are obtained from the prototype power converter and the key contributions are summarized.

Chapter 3 describes a duty-cycle sensor for current-sensing applications in power converters. It presents the proposed architecture and its evolution. The circuit implementation details are discussed. The measured results from a prototype duty-cycle sensor are presented and the key contributions are summed up.

Chapter 4 describes a temperature compensated relaxation oscillator. The

proposed architecture is explained and an analysis is presented about the residual temperature error using this approach. The circuit details are explained clearly. Measured results from the prototype are shown and the principal contributions are highlighted.

Finally, Chapter 5 summarises the proposed design techniques for integrated energy-efficient power converters and some possible future work is outlined.

## CHAPTER 2

# A 91.15% EFFICIENT 2.3-5 V INPUT 10-35 V OUTPUT HYBRID BOOST CONVERTER FOR LED-DRIVER APPLICATIONS

### 2.1 Introduction

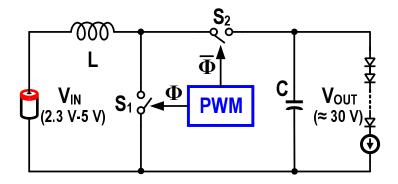

Rapid technological advances over the last decade have made the display module an integral part of modern portable electronic devices such as smartphones and tablets. While these developments have enhanced user experience significantly, they also made the displays by far the most power-hungry blocks in smartphones [6]. A typical display module comprises a back-light and an LCD panel. The back-light consists of strings of series-connected white light-emitting diodes (LEDs). Screen size and brightness requirements may mandate stacking of up to eight LEDs in each string. With each LED having a forward-bias voltage of about 3.3 V, the required supply voltage needed to drive the chain can be as high as 27 V. Tight volume constraints mandate that such a high output voltage be generated from a 2.3-5 V input voltage provided by a Li-ion battery. To this end, a boost converter is most commonly used to perform the desired DC-to-DC conversion. Since the display module consumes 30-40% [6] of the total available energy, the efficiency of such a boost converter significantly impacts system power efficiency. Traditionally, an inductor-based switching power converter depicted in Fig. 2.1 is used [7]. It consists of a pair of switches  $S_1$ ,  $S_2$ , an inductor L, and an output capacitor C. Switches  $S_1$  and  $S_2$  are driven by complementary PWM signals with a duty-cycle of D and (1-D) and generates an output voltage given by Eq. 2.1:

$$V_{\text{OUT}} = \frac{V_{\text{IN}}}{1 - D}.\tag{2.1}$$

<sup>© 2021</sup> Nilanjan Pal. Reprinted, with permission, from N. Pal *et al.*, "A 91.15% Efficient 2.3-5 V Input 10-35 V Output Hybrid Boost Converter for LED-Driver Applications," *IEEE Journal of Solid-State Circuits*, Jul 2021 [5].

Figure 2.1: Conventional boost converter-based LED driver.

Even though this architecture requires very few off-chip components, its efficiency is fundamentally limited by the switches' high voltage rating. As will be described later, a high switch rating exacerbates both switching and conduction losses, thus limiting the achievable peak efficiency of state-of-theart display drivers to about 88% [7, 8].

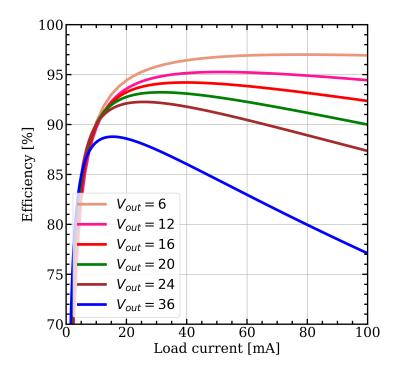

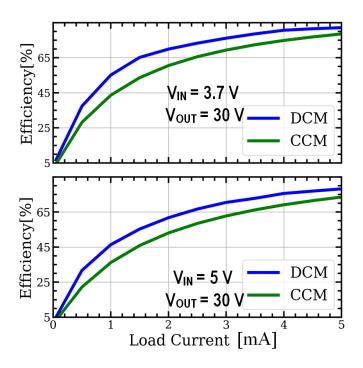

The impact of switch voltage rating on boost converter efficiency can be understood by plotting efficiency versus load current for different output voltages at a fixed input voltage (see Fig. 2.2). The power switch sizes were optimized for each output voltage. As the switch rating increases (to support the increased output voltage) from 6 V to 36 V, peak efficiency degrades by more than 5%. The reduction in the power switch quality increases both the switching and conduction losses, which causes the observed degradation in peak efficiency. One possible approach to overcome this problem would be to explore architectures that do not require such high voltage-rated switches. A class of switched capacitor (SC)-based converters can generate high output voltages using devices rated lower than the output voltage [9], [10]. But they incur a considerable amount of charge-sharing losses at typical LED driver's operating power levels. The large DC gain requirement increases the number of switches, which significantly increases conduction and switching losses.

Hybrid architectures have recently emerged as an alternative to the SC-based approaches mentioned above. By cascading a SC stage with an inductive stage [1] or by merely placing an inductor between the power source and a SC converter [11], [12], these architectures seek to combine the advantages of inductive- and SC-based converters. Placing the inductor in the path of the charging/discharging current of the flying capacitor reduces hard-charging losses to a great extent. Recent works have effectively used

Figure 2.2: LED driver efficiency versus load current for different output voltages and fixed  $V_{IN} = 3.7 \text{ V}$ .

this approach, but could not completely eliminate hard-charging losses [13] or output-voltage rated switches [14].

This paper presents a high-efficiency boost converter for LED driver applications with an input voltage range of 2.3-5 V, an output voltage range of 10-35 V, and a load range of 0-100 mA [15]. The prototype power converter was fabricated in 180 nm technology and occupies an active area of 2.3 mm by 1.2 mm, and operates at 1 MHz switching frequency. The power converter achieves an excellent peak power-efficiency of 91.15% at 3.7 V input, 30 V output with no external gate driver supplies, representing a 3% improvement in peak efficiency over the state-of-the-art. This paper supplements the information provided in [15] with a detailed elucidation of the architecture evolution, an in-depth analysis of the output impedance of hybrid architectures, a detailed description of the phase-by-phase operation of the converter, additional details of the zero-crossing detector for discontinuous conduction mode (DCM) operation, and new measurement results pertaining to the improvement in power efficiency in DCM compared to CCM.

The rest of the paper is organized as follows: Section 2.2 presents a breakdown of the losses in an inductive boost converter used in conventional LED drivers; Section 2.3 presents the proposed architecture; circuit implementation details of key building blocks are described in Section 2.4; experimental results from the test chip are presented in Section 2.5; key contributions of this paper are summarized in Section 2.6.

### 2.2 LED driver losses

Losses in a LED driver depend on the magnitude of input/output voltages, load current, and switching frequency. The typical range of input/output voltages and load current is 2.3-5 V/12-30 V and 0-100 mA, respectively. Losses can be broadly classified as conduction losses and switching losses. The current source used to set the LED current has to biased with about 200 mV across it, which also incurs an efficiency penalty. However, in LED drivers with  $V_{OUT}$  as high as 30 V, the efficiency hit is minimal. These loss mechanisms are investigated for the conventional inductive boost converter next and later extended to the proposed architecture.

Conduction losses are modeled using the below equation [16]:

$$P_{cond} = i_{IND,RMS}^{2} \cdot (R_{DCR} + D \cdot R_{LS} + (1 - D) \cdot R_{HS} + R_{PCB})$$

(2.2)

where,  $i_{IND,RMS}$  is the inductor RMS current, D is the duty-cycle of the low-side switch and  $R_{LS}$ ,  $R_{HS}$  are the "on" resistances of the low- and high-side switches, respectively. The value of  $R_{DCR}$  depends on the size of the inductor and is typically in the range of 200-300 m $\Omega$ s for inductors used in space-constrained mobile applications. Such a large  $R_{DCR}$  is a significant source of conduction loss, especially at higher load currents.

Switching losses have three components denoted by  $P_{transition}$ ,  $P_{gate}$ , and  $P_{core}$ . Power switch losses incurred during transitions between "on" state and "off" state is represented by  $P_{transition}$ . This is a result of the current through the power device and the voltage across the power device being non-zero during the transition.

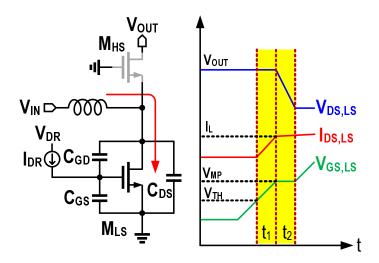

Using low-side switch  $M_{LS}$  voltage and current waveforms during a turn-ON event (see Fig. 2.3),  $P_{transition}$  can be calculated using Eq. 2.3 [17, 18, 19, 20, 21, 22, 23, 24]:

$$P_{transition} = 0.5 \cdot F_{SW} \cdot V_{OUT} \cdot I_L \cdot (t_1 + t_2) \tag{2.3}$$

where  $V_{OUT}$  is the output voltage,  $F_{SW}$  is the inductor switching frequency. Times  $t_1$  and  $t_2$  are estimated using gate driver current  $I_{DR}$  and gate charges  $Q_{GS}$  and  $Q_{GD}$  as explained in [19]. At large load currents,  $P_{transition}$  becomes a significant component of the switching losses. This transition loss equation can be modified to include the reverse recovery loss of the body diode of  $M_{HS}$  and that of the parasitic capacitance  $C_{DS,LS}$  [25].

Figure 2.3: Transition loss modeling for turn-ON event of low-side switch.

$P_{gate}$  represents the power lost during the charging/discharging of the gate terminal of the power switches and can be modeled by Eq. 2.4 [16]:

$$P_{qate} = C_{qate} \cdot V_{IN}^2 \cdot F_{SW} \tag{2.4}$$

where  $C_{gate}$  and  $V_{IN}$  is the gate capacitance of the power switch and input voltage to the power converter, respectively.

$P_{core}$  represents the inductor's magnetic losses, and its magnitude depends on the inductor dimensions, with larger height inductors having lower core losses. Core losses can be calculated using Steinmetz expression in Eq. 2.5 [26]

$$P_{core} = K_{FIT} \cdot F_{SW}^{\alpha} \cdot (\Delta I_{IND})^{\beta} \tag{2.5}$$

where  $K_{FIT}$ ,  $\alpha$  and  $\beta$  are fitting parameters provided by manufacturers.  $\Delta I_{IND}$  is inductor current ripple. In addition to the losses described above, other losses, such as dead-time losses, are also incurred during every switching cycle, but their contribution to the total loss is much smaller.

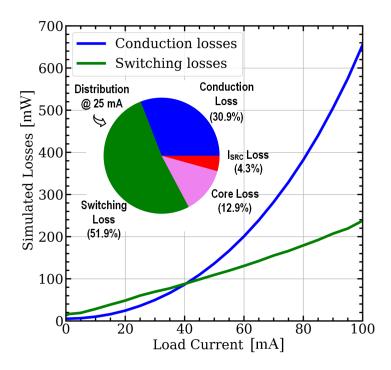

### 2.2.1 Simulated loss breakdown

The power converter's efficiency is typically optimized at the most probable load current, which is around 20-40 mA for LED drivers used in smartphones [27]. A 3.7 V input 30 V output conventional inductive boost power converter was designed to examine the relative contribution of each type of loss, and the simulated variation of conduction and switching losses as a function of the load current is plotted in Fig. 2.4. Switch sizes were chosen to minimize the total loss (switching + conduction) for a given load current and switching frequency. The pie-chart in Fig. 2.4 shows the relative contribution of each type of losses at 25 mA load current, incuding the current source losses ( $I_{SRC}$  losses). Both the switching and conduction losses contribute significant portions to the total loss at this load current. Because power switch size trades off conduction losses with switching losses, increasing the switch size beyond a certain point does not reduce the total loss. Architectures that allows switches with lower voltage rating ease this trade-off, thereby presenting a possibility for significantly reducing the losses.

## 2.3 Proposed Architecture

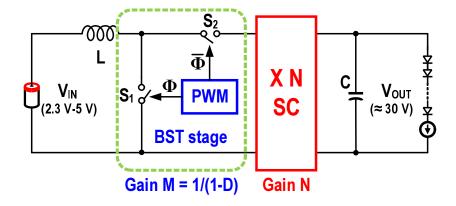

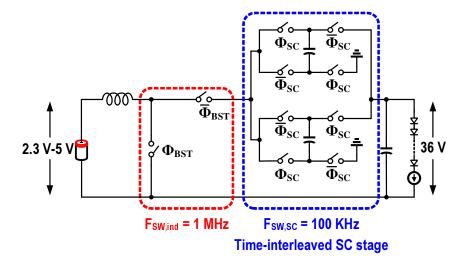

A simplified block diagram of the proposed hybrid boost converter architecture is shown in Fig. 2.5. It consists of an inductive boost stage (BST) followed by a switched-capacitor (SC) stage. The BST stage provides a DC gain of M = 1/(1-D), where D is the PWM signal's duty-cycle while, SC

Figure 2.4: Electrical switching loss  $(P_{transition} + P_{gate})$  and conduction loss variation with load current and loss breakdown at 25 mA load  $(V_{IN} = 3.7 \text{ V}, V_{OUT} = 30 \text{ V})$  for a conventional inductive-boost power converter.

stage provides a DC gain of N. DC gains, M, N, must be chosen to meet the overall DC gain requirement, which in our application is about 10. Therefore, for instance, M=5 and N=2 would satisfy this requirement. With this choice, all the switches in BST and SC stages experience a maximum voltage of only half the output voltage across them. Thus, switches rated for only 15 V (as opposed to 30 V) can be used. While the proposed architecture has successfully reduced the power switches' voltage rating, the total number of switches has increased. However, with the appropriate choice of the SC stage architecture and its switching frequency, it is possible to achieve better efficiency, as described next.

### 2.3.1 SC-stage architecture selection

Two important considerations dictate the choice of SC-stage architecture. First, power losses must be low enough not to impact the overall converter

Figure 2.5: Hybrid boost converter.

efficiency. Second, the architecture must be amenable for simple circuit implementation and must obviate the need for auxiliary power supplies. A series-parallel architecture shown in Fig. 2.6 meets these criteria. The lowest output impedance is achieved across a wide range of DC gains when this architecture is operated in the fast-switching limit region where losses associated with switch resistance dominate [10]. The optimal distribution

Figure 2.6: Proposed boost converter topology.

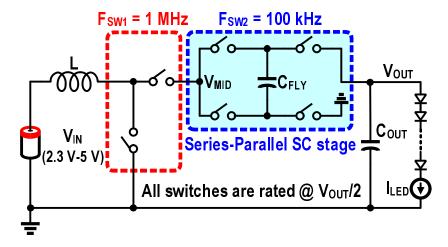

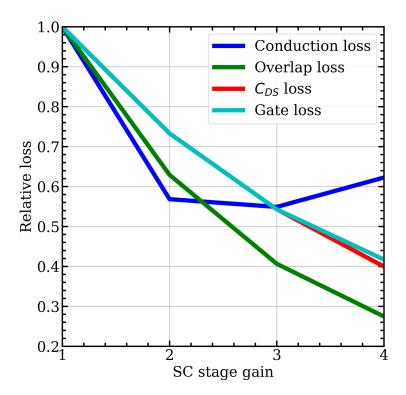

of the total DC gain between the inductive-boost and SC stages is determined using the approach described in [14]. In this analysis, output voltage and the conversion gain are set at 30 V and 10, respectively; SC stage was assumed to employ series-parallel architecture. The hybrid converter was optimized for each value of SC-stage gain (N) while keeping the area of the power converter, and the ratio of input/output voltages fixed to perform a

fair comparison. Conduction and switching losses normalized to the losses of a conventional inductive-based power-converter are plotted for different values of N, as shown in Fig. 2.7. Switching losses reduce as N (SC-stage gain) is increased. This is expected behavior since the dominant source of switching loss, namely switching losses in the inductive-boost stage, reduces with increasing N. This is because the rating of the switches in the BST-stage is inversely proportional to the SC stage gain N ( $V_{OUT}/N$ ). But the same is not true for conduction losses, which reduce when N is changed from N = 1 to N = 2 but start increasing from N = 3. This shows that the increased number of switches offsets the advantage obtained in going to lower-rated switches as N is increased beyond 3. Therefore, N is chosen to be 2 in our implementation. This topology needs only four extra switches, all of which are rated at  $V_{OUT}/2$ . Their gate drivers can be implemented using internally available voltages, as described in section 2.4.

Figure 2.7: Relative loss of proposed architecture with SC-stage gain varying from 2 to 4, normalised to corresponding losses in conventional inductive-boost converter.

# 2.3.2 Choice of switching frequency for the BST and SC stages

The switching frequency of a conventional inductive boost converter is determined from the ripple requirement, allowed output capacitor, and the load current. Assuming typical parameters of 10  $\mu$ F (400 nF after de-rating) output capacitor, 25 mA load current, and an output voltage ripple of 50 mV results in a switching frequency of 1 MHz for the BST stage.

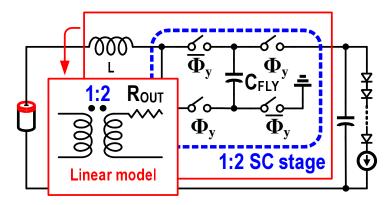

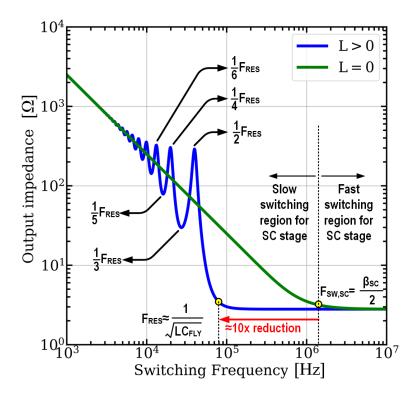

For a typical switched-capacitor power converter with a voltage input, the switching frequency directly impacts the loss of the converter. This can be understood by modeling losses in the 1:2 SC converter with an ideal transformer and an output impedance  $R_{OUT}$  (see Fig. 2.8) [10] [28] [29] and plotting  $R_{OUT}$  as a function of switching frequency for two cases: L=0 and  $L\neq 0$  as shown in Fig. 2.9. For the case of L=0, output impedance  $R_{OUT,SC}$  is given by Eq. 2.6.

Figure 2.8: 1:2 switched-capacitor converter with inductor at input.

$$R_{\text{OUT,SC}} = \frac{1}{C_{\text{FLY}} F_{\text{SW,SC}}} * \coth \frac{\beta_{\text{SC}}}{4 F_{\text{SW,SC}}}$$

(2.6)

where,

$$\beta_{\rm SC} = \frac{1}{R_{\rm SW,TOT}C_{\rm FLY}}$$

$$R_{\rm SW,TOT} = 2*R_{\rm SW}$$

and  $R_{\text{SW,TOT}}$  is the total switch resistance in the charging/discharging path,  $R_{\text{SW}}$  is switch resistance and  $F_{SW,SC}$  is the switching frequency. The converter operates in the slow-switching limit for switching frequencies below 1

MHz. In this region, charge sharing losses account for the increase in  $R_{OUT}$  with decreasing switching frequency. Beyond 1 MHz, losses associated with the switch resistance dominate, as indicated by the flattening of the curve.

Figure 2.9: Comparison of output impedance of basic hybrid converter with that of the traditional switched-cap converter.

Inductance between the input voltage source and the converter fundamentally changes the relationship between output impedance and the switching frequency. Because inductor current cannot change instantaneously, sudden surges in capacitor-charging currents present when L=0 are avoided, thus, significantly reducing the charge sharing losses. The output impedance of the hybrid converter is determined by calculating the ratio of average power dissipated  $\langle P_{\rm HYB} \rangle_{T_{\rm sw}}$  and the average output current  $\langle I_{\rm OUT,HYB} \rangle_{T_{\rm sw}}$  in each switching cycle as given by Eq. 2.7:

$$R_{\rm OUT, HYB} = \frac{\langle P_{\rm HYB} \rangle_{T_{\rm sw}}}{\langle I_{\rm OUT, HYB} \rangle_{T_{\rm sw}}^2}$$

(2.7)

where,

$$\langle P_{\rm HYB} \rangle_{T_{\rm sw}} = 2F_{\rm SW,SC}(T_1 + T_2 + T_3)$$

$$T_1 = 0.5(k_1^2 + k_2^2)R_{\rm SW,TOT} \frac{1 - e^{-\alpha T_{\rm sw}}}{2\alpha}$$

$$T_2 = \frac{\alpha B + \beta_{\rm HYB}C}{2(\alpha^2 + \beta_{\rm HYB}^2)} (1 - e^{-\alpha T_{\rm sw}} \cos(\beta_{\rm HYB}T_{\rm sw}))$$

$$T_3 = \frac{\beta_{\rm HYB}B - \alpha C}{2(\alpha^2 + \beta_{\rm HYB}^2)} e^{-\alpha T_{\rm sw}} \sin(\beta_{\rm HYB}T_{\rm sw})$$

$$\langle I_{\rm OUT,HYB} \rangle_{T_{\rm sw}} = F_{\rm SW,SC}(P_1 + P_2)$$

$$P_1 = \frac{\beta_{\rm HYB}k_1 + \alpha k_2}{\alpha^2 + \beta_{\rm HYB}^2} (1 - e^{-\alpha T_{\rm sw}} \cos(\beta_{\rm HYB}T_{\rm sw}))$$

$$P_2 = \frac{\beta_{\rm HYB}k_2 - \alpha k_1}{\alpha^2 + \beta_{\rm HYB}^2} e^{-\alpha T_{\rm sw}} \sin(\beta_{\rm HYB}T_{\rm sw})$$

$$B = 0.5(k_2^2 - k_1^2)R_{\rm SW,TOT}$$

$$C = k_1k_2R_{\rm SW,TOT}$$

$$k_1 = \frac{\alpha I_{\rm LOAD}}{\beta_{\rm HYB}}$$

$$k_2 = I_{\rm LOAD}$$

$$\alpha = \frac{R_{\rm SW,TOT}}{2L}$$

$$\beta_{\rm HYB} = \sqrt{\frac{1}{LC_{\rm FLY}} - \left(\frac{R_{\rm SW,TOT}}{2L}\right)^2}$$

$$\Delta V = \frac{0.5I_{\rm LOAD}T_{\rm sw}}{C_{\rm FLY}}$$

The relationship between  $R_{\rm OUT, HYB}$  and the switching frequency is more complicated compared to the L=0 case (see Fig. 2.9). At frequencies much lower than the LC-resonant frequency ( $F_{RES}=\sqrt{LC_{\rm FLY}}/(2\pi)$ ), the current transient settles down well within the duration of each phase, thereby having no impact on  $R_{OUT}$ . As the switching frequency approaches  $F_{RES}$ ,  $R_{OUT}$  exhibits a non-monotonic behavior with peaks at  $F_{RES}/2$ ,  $F_{RES}/4$ ,  $F_{RES}/6$  and so on, and troughs at  $F_{RES}/3$ ,  $F_{RES}/5$ ,  $F_{RES}/7$  and so on. Beyond  $F_{RES}$ , charge-sharing losses again fall below the resistive losses of the switches. With proper choice of L and C,  $F_{RES}$  can be reduced to be much lower than transition frequency for the L=0 case.

In this work,  $C_{FLY}$  was set equal to the expected output capacitance

Figure 2.10: Time-interleaving of the SC stage to mitigate large output voltage ripple.

of 400 nF (de-rated) and the inductance is equal to 10  $\mu$ H. Figure 2.9 shows  $F_{RES}$  is 10x lower compared to the L=0 case. It is worth noting that the resonance frequency will be much lower than what is predicted by the above analysis because the inductor is switched and will be equal to  $F_{RES,SWITCHED} = F_{RES} * (1 - D)$ , where D is the duty cycle with which the inductor is switched. Consequently, it would seem like the SC-stage can be switched at much lower frequency than 70 kHz. But, lowering the switching frequency increases the inductor RMS current significantly, which increases the conduction losses. Because of this tradeoff, losses due to inductor RMS current and the switching losses in the SC-stage are better balanced when  $F_{SW,SC} = F_{RES}$ . Another practical consideration in choosing  $F_{SW,SC}$  involves preventing the inductor from being connected to the SC stage when the flying capacitors are changing phases. This can be guaranteed if  $F_{SW,SC}$  is made an integer sub-multiple of  $F_{SW,BST}$ . Thus, considering the above,  $F_{SW,SC}$  was chosen to be 100 kHz, which is the closest sub-multiple of  $F_{SW,BST}$  (1 MHz).

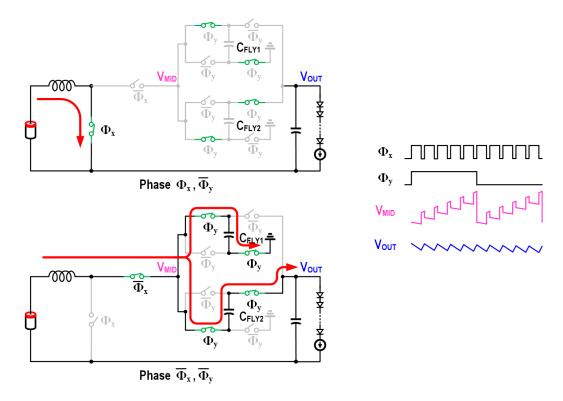

### 2.3.3 Time-interleaved SC stage

While operating the SC-stage at 100 kHz can potentially reduce its switching losses, it has a detrimental effect on the output ripple. For instance, a 50% duty cycle 100 kHz clock for the SC stage results in the output capacitor floating for a duration of 5  $\mu$ s, which results in an unacceptably large peak-

Figure 2.11: Efficiency plots of the hybrid and conventional architectures.

to-peak ripple of 0.25 V at a typical load of 25 mA and a worst-case ripple of 1 V at 100 mA load with 0.5  $\mu$ F output capacitance. In conventional boost converters, the headroom of the LED bias current source must be increased (V<sub>HR</sub> = V<sub>D,SAT</sub> + V<sub>RIPPLE</sub>) to absorb the excessive ripple and prevent it from affecting the backlight quality. However, this degrades LED driver power efficiency and causes perceivable flicker in the backlight. One possible way to avoid this large ripple is to ensure the lost charge in the output capacitor is replenished faster. This can be achieved by splitting the single SC-stage into two time-interleaved sections that alternately connect to the output capacitor. The operation of the converter is described in detail in section 2.3.5. The final architecture of the proposed boost converter is shown

Figure 2.12: Switching loss comparison.

in Fig. 2.10. It consists of 10 power switches, all rated at  $V_{OUT}/2$ , and two additional external flying capacitors  $C_{FLY}$ .

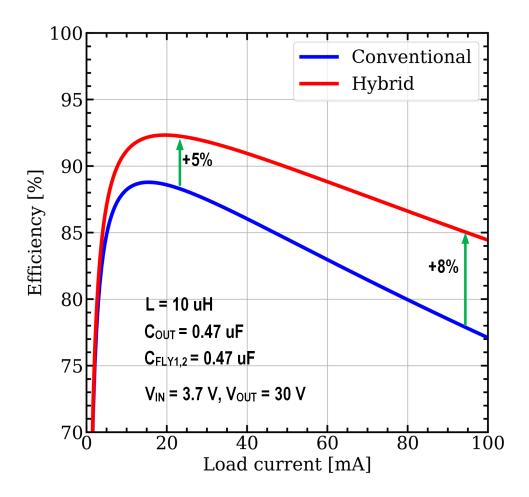

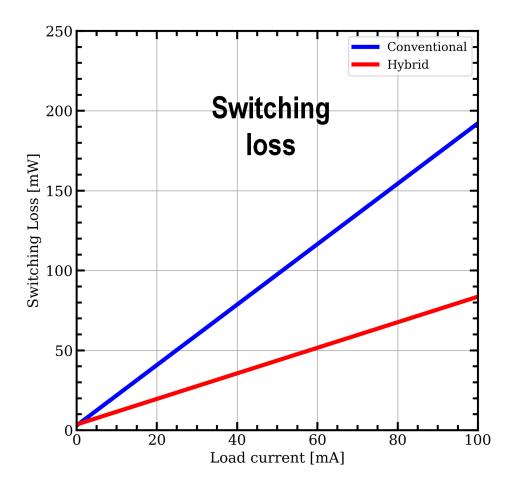

## 2.3.4 Efficiency and loss breakdown

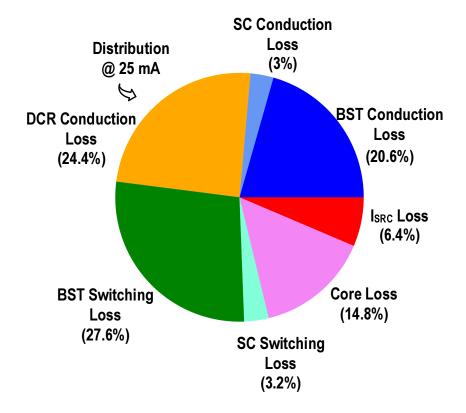

Theoretical power efficiency plots comparing the proposed hybrid boost converter with the conventional boost converter are shown in Fig. 2.11(a). These plots show a marked improvement in efficiency across the entire load range with about 5% and 8% peak efficiency improvement at nominal and high loads, respectively. The improvement in conduction and switching losses are captured in Figs. 2.11(b) and (c). They show a significant reduction in

Figure 2.13: Conduction loss comparison.

switching losses and modest improvement in conduction losses, both of which illustrate that higher quality switches and the SC stage's low switching frequency indeed help improve efficiency. The simulated power loss breakdown for the proposed converter at 25 mA load is depicted in Fig. 2.14, and the percentage reduction in losses normalized to those of a conventional inductive boost converter is shown in Table 2.1.

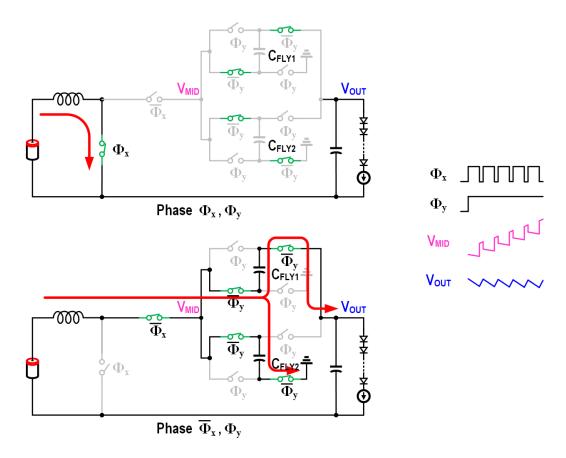

### 2.3.5 Phase operation

The converter operates in four phases,  $\Phi_1$ ,  $\Phi_2$ ,  $\Phi_3$ , and  $\Phi_4$  (see Fig. 2.15 and 2.16).

Table 2.1: Percentage reduction in losses with respect to conventional inductive boost converter

| Loss       | % Reduction | Cause                           |

|------------|-------------|---------------------------------|

| Conduction | 30          | Device rating                   |

| Switching  | 52          | Device rating+low $F_{SW,SC}$   |

| Core       | 22.6        | Inductor current ripple reduced |

Figure 2.14: Simulated power loss breakdown at 25 mA load for the proposed converter.

We describe the operation starting with phase  $\Phi_1$  in which both the boostand SC-stage clocks  $\phi_{\rm BST}$  and  $\phi_{\rm SC}$  are high. During this phase, inductor and  $C_{FLY2}$  are connected to the ground while  $C_{FLY1}$  is connected to the output. The duration of this phase is equal to  $D*T_{\rm BST}$  where D is the duty-cycle of the clock  $\phi_{\rm BST}$ , and  $T_{\rm BST}$  is the period of  $\phi_{\rm BST}$ . Because the inductor is disconnected from the load, the LED current source discharges the output capacitor. When  $\phi_{\rm BST}$  goes low, the converter enters  $\Phi_2$  phase during which inductor is connected to the SC stage. As  $V_{\rm OUT} = 2*V_{\rm MID}$ , half the inductor current flows through the output capacitor through  $C_{FLY1}$  and the other half flows through  $C_{FLY2}$ . This causes  $V_{MID}$  voltage to ramp-up as shown in the

Figure 2.15: Phase-by-phase operation and associated waveforms for phase  $\phi_y$ .

waveforms on the right in Fig. 2.15 and Fig. 2.16. The kink in the ramp is caused by the voltage drop across the power devices in the SC stages. Since switching frequency of the SC stage is much smaller than the BST stage,  $\phi_{\text{BST}}$  changes its phase five times in one half of  $\phi_{\text{SC}}$ . Consequently  $C_{FLY1}$  and  $C_{FLY2}$  gets discharged and charged, respectively five times during  $\Phi_2$ .

In  $\Phi_3$  phase,  $C_{FLY1}$  and  $C_{FLY2}$  exchange positions. Since the voltages across  $C_{FLY1}$  and  $C_{FLY2}$  always add up-to  $V_{OUT}$ , this change in positions of the flying capacitors do not affect the output voltage. The voltage at  $V_{MID}$  on the other hand always reflects voltage across  $C_{FLY2}$  in  $\phi_{SC}$  and across  $C_{FLY1}$  in  $\overline{\phi_{SC}}$ . This node experiences a voltage jump when the flying capacitors exchange their positions because the inductor current cannot change suddenly. The voltage jump's magnitude is equal to the voltage difference between the voltages across  $C_{FLY1}$  and  $C_{FLY2}$  at the end of  $\Phi_2$ . After this change in flying capacitor positions, rest of the operation is exactly same as described before, except now for the next five cycles of  $\phi_{BST}$ ,  $C_{FLY1}$  is

Figure 2.16: Phase-by-phase operation and associated waveforms for phase  $\overline{\phi_y}$ .

charged and the inductor current discharges  $C_{FLY2}$ . This marks the end of one complete cycle of  $\phi_{SC}$ . The BST stage provides a DC gain of 1/(1-D), and the SC stage provides a gain of two. Therefore the relation between the output voltage and the BST stage's duty cycle is given by 2/(1-D).

# 2.4 Circuit Implementation

The complete schematic of the proposed converter is shown in Fig. 2.17 and 2.18. It consists of three main components: the power devices used in the BST and SC stages, the gate drivers for these power devices, and circuitry to regulate the converter's output voltage.

#### 2.4.1 Power switches

All the power devices in this architecture are rated at 20 V. The maximum voltage-stress seen by each switch is given by  $V_{OUT,max}/2 + I_{OUT,max} * 0.25 *$

Figure 2.17: Full circuit schematic.

$T_{SW,SC}/C_{FLY}$ , and is equal to 18.6 V.  $T_{SW,SC}$  (1/ $F_{SW,SC}$ ) is the switching period of the SC-stage. Switch sizing was optimized to achieve peak efficiency at  $I_{LOAD}=25$  mA. The BST stage's low-side switch is sized for an  $r_{DS,ON}$  of 123 m $\Omega$ , while the rest of the switches are sized for an  $r_{DS,ON}$  of 350 m $\Omega$ . The power devices occupy an area of 2.76 mm<sup>2</sup>. Flip-chip packaging and careful routing of the power rails at both the chip and the PCB level were employed to reduce parasitic resistance and inductance.

#### 2.4.2 Gate drivers

The interleaved SC stage limits the maximum voltage across the power switches to  $V_{OUT}/2$ , enabling the use of devices rated at  $V_{OUT}/2$  with lower  $R_{DS,ON}$  and smaller parasitic capacitance. Leveraging this topological benefit for improving efficiency without affecting device reliability requires carefully-designed gate driver circuits. Figure 2.17 and Fig. 2.18 shows these circuits used for driving power devices,  $M_2$ ,  $M_{3A/B}$ ,  $M_{4A/B}$ ,  $M_{5A/B}$  and  $M_{6A/B}$ , with the desired voltage levels of  $V_{SW}$ -to- $(V_{SW} + V_{IN})$ ,  $V_{MID}$ -to- $(V_{MID} + V_{IN})$ ,  $V_{BOTA/B}$ -to- $(V_{BOTA/B} + V_{IN})$ ,  $(V_{OUT} - V_{IN})$ -to- $V_{OUT}$  and 0-to- $V_{IN}$ , respectively. Drivers for  $M_1$  and  $M_6$  are implemented using tapered buffers oper-

Figure 2.18: Gate-driver details for power devices.

ating with  $V_{IN}$  as their supply.  $M_2$  ( $M_{4A/B}$ ) driver is implemented using a dynamic level-shifter [30] with bottom-plate of the boot-strapping capacitor  $C_{BOOT2}$  ( $C_{BOOT4A/B}$ ) connected to  $V_{SW}$  ( $V_{BOT1/2}$ ). Transistor  $M_X$  (rated at  $V_{IN} + V_{OUT}/2$ ) and pull-up resistor  $R_{PU}$  are sized such that swing at the inverter ( $INV_{1/2}$ ) input is about  $V_{IN}$ . To minimize static power, input PWM signal is converted into two narrow pulses and recovered using an SR latch.  $M_3$  and  $M_5$  drivers are implemented using capacitively-coupled level-shifters [30] wherein coupling capacitors  $C_{C3}$  and  $C_{C5}$  hold voltages  $V_{MID}$  and  $V_{OUT}$ , respectively. Pull-up resistors pre-charge capacitors ( $C_{C3/5}$ ) to the

required voltage levels before the start of each switching cycle. The coupling capacitors  $C_{C3}$ ,  $C_{C5}$  and the boot-strap capacitors  $C_{BOOT2}$  ( $C_{BOOT4A/B}$ ) are off-chip as they needed to be about 10 times the gate capacitance of the power device they were driving. Both the bootstrap and coupling capacitors are implemented using 1.5 nF 0201 packaged surface-mount capacitors (0.02 in. X 0.01 in.).

#### 2.4.3 Regulation loop

A voltage-mode integral-control loop is used for regulating the output voltage. Note that a current source sets the LED current, and as a result, using a voltage-mode compensator has no bearing on the LED bias current as long as the output voltage is sufficiently high to forward bias all the LEDs and guarantee the desired voltage headroom for the current source. A transconductance-C stage integrates the difference between the converter output voltage and the reference voltage and generates a control voltage  $(V_{CTRL})$ . The value of compensation capacitor  $C_C$  is equal to 20 nF and it is implemented off-chip. PWM comparator compares V<sub>CTRL</sub> with an externally fed 1 MHz saw-tooth signal and produces a duty-cycle for the low-side device of the BST stage. The loop bandwidth is about 1 kHz. The clock for the SC stage is generated by dividing the BST stage PWM signal by 10. A ring counter that generates a divide-by-five clock followed by a divide-by-two stage produces the divided-by-10 signal (100 kHz) with 50% duty-cycle. The small-signal model for the proposed architecture has been derived based on the procedure in [16] and is shown below in Fig. 2.19. The duty-cycle to  $V_{OUT}$  transfer function is given by Eq. 2.8:

$$G_{vd} = \frac{V_{OUT,DC}}{2D'} \frac{1 - s \frac{4L}{D'^2 R_L}}{1 + s \left(\frac{4L}{D'^2 R_L} + \frac{4C_{OUT}R_{eq}}{D'^2}\right) + s^2 \frac{4LC_{OUT}}{D'^2}}$$

(2.8)

where, D'=1-D, D being the duty-cycle of the low-side switch of the BST stage.

Figure 2.19: Small-signal model for the proposed architecture in continuous conduction mode.

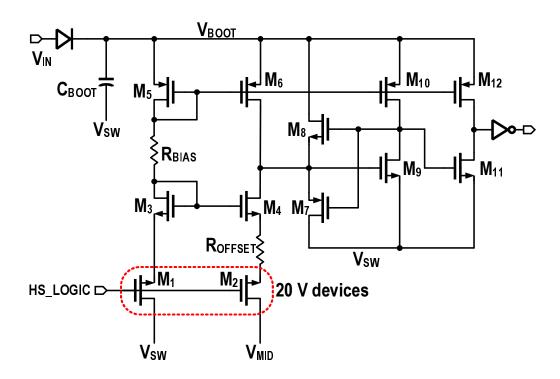

#### 2.4.4 Discontinuous conduction mode

The converter was operated in the discontinuous conduction mode to improve the efficiency under light-load conditions (less than 5 mA). A zero-crossing

Figure 2.20: Zero-crossing detector circuit used in the discontinuous conduction mode.

detector circuit shown in Fig. 2.20 detects the voltage drop across the highside power device and translates it to current. This voltage drop appears as difference in  $V_{GS}$  of  $M_3$  and  $M_4$  which is then converted into a current equal to  $i_{SENSE} = g_{M3,4} \Delta V_{GS}$ . Trans-impedance amplifier (TIA) implemented using  $M_7, M_8, M_9$  and  $M_{10}$  transistors along with the post amplifier ( $M_{11}$  and  $M_{12}$ ) convert  $i_{SENSE}$  into a rail-to-rail voltage output.  $R_{BIAS}$  is used to generate an internal bias current, and  $R_{OFFSET}$  is used to create an intentional offset to account for the delay in the zero-crossing detector.  $M_1$  and  $M_2$  act as shielding devices to protect rest of the 5 V devices when the  $V_{SW}$  node goes to ground potential. The DCM mode improves efficiency by about 10% over the CCM mode at loads near 1 mA.

#### 2.5 Measurement Results

A prototype converter was fabricated in a 180 nm process and attached to the test board using a flip-chip package (see Fig. 2.21). Active area is  $2.8 \text{ } mm^2$ .

Figure 2.21: Die micrograph and evaluation board.

Flying capacitors ( $C_{FLY1}$  and  $C_{FLY2}$ ) were placed very close to the chip. During start-up, since all the initial flying-capacitor voltages are much lower than their steady-state values, the inductor current increases in both its switching phases, resulting in huge initial inductor current of the order of 2 A (see Fig. 2.25). Since the voltage at  $V_{MID}$  toggles between the two flying capacitor voltages, the initial inductor current surge can cause voltage at node  $V_{MID}$  to exceed the device rating. To avoid this, the SC-stage switching frequency is initially increased to 500 kHz, which is five times the steady-state switching frequency and reduced back to 100 kHz after  $C_{FLY,1}$  and  $C_{FLY,2}$  are charged to  $V_{OUT}/2$  and the output capacitor is charged to  $V_{OUT}$ . In addition to the fast SC-stage switching during start-up, it would also be beneficial to employ an over-current protection scheme to limit the inductor current under

Figure 2.22: Steady-state waveforms in CCM.

Figure 2.23: Steady-state waveforms in DCM.

a safe value. To this end, a simple over-current protection scheme based on a conventional resistor-based current sensing at the LS power-FET of the BST stage [31] can be employed. Current sensing can also be performed

Figure 2.24: Steady-state ripple in CCM at 25 mA load.

Figure 2.25: Start-up waveforms for  $V_{OUT},\,V_{MID}$  and  $I_{IND}.$

by a sense-FET based current sensor [32] by placing the sense-FET across the LS power-FET of the BST stage. Relevant steady-state voltages of the converter with  $V_{IN}=3.7$  V,  $V_{OUT}=30$  V and  $I_{LED}=25$  mA in both CCM and DCM modes are shown in Fig. 2.22 and Fig. 2.23, respectively.

Figure 2.26: Start-up waveforms for  $V_{OUT}$ ,  $V_{MID}$  and  $I_{IND}$ , zoomed.

Figure 2.27: Transient response waveforms for  $V_{OUT}$ .

Output voltage  $(V_{\rm OUT})$ , switching node of the BST stage  $(V_{\rm SW})$ , voltage at the intermediate node between the BST and the SC stages  $(V_{\rm MID})$  along with the inductor current  $(I_{\rm L})$  waveforms are shown.  $V_{\rm OUT}$  and  $V_{\rm MID}$  have settled at 30 V and 15 V respectively for both CCM and DCM operations. In the DCM operation, the ZCD circuit cuts off the high-side switch when the current through it crosses zero. This results in oscillations in  $V_{\rm SW}$  and  $I_{\rm L}$  as shown in Fig. 2.23, because the parasitic capacitance at  $V_{\rm SW}$  node was still charged to  $V_{\rm OUT}$  after the high side switch was turned-off. This provided a non-zero initial condition to the LC tank formed by the parasitic capacitance at  $V_{\rm SW}$  and inductor L. This results in a small undershoot below zero, in the inductor current.

Table 2.2: Performance summary and comparison to state-of-the-art LED drivers.

|                                      | This Work                     | Work                    | LM36274 [33]            | LM36923 [7]               | JSSC '20 [14]   | TPE '19 [13]            | TPS6118 [8]               |

|--------------------------------------|-------------------------------|-------------------------|-------------------------|---------------------------|-----------------|-------------------------|---------------------------|

| Technology                           | 180 nm BCL                    | BCD                     | 180 nm BCD              | 180 nm BCD                | 350 nm CMOS     | ı                       | I                         |

| Input Volt. [V]                      | 2.3-5                         | -5                      | 2.7-5                   | 2.7-5                     | 2-4.4           | 6-18                    | 5-24                      |

| Max Output Volt. [V]                 | 35                            | 2                       | 29                      | 28                        | 20              | 50                      | 40                        |

| Load Range [mA]                      | 0-100                         | 001                     | 0-100                   | 0-100                     | 10-250          | 70-100                  | 0-120                     |

| Conversion Ratio                     | 2/(1-D)                       | -D)                     | 1/(1-D)                 | 1/(1-D)                   | 2/(1-D)         | (3-D)/(1-D)             | 1/(1-D)                   |

| Switching Freq.[Hz]                  | $1 \mathrm{M}/100 \mathrm{K}$ | .00 K                   | 1 M                     | 1 M                       | 2 M             | $\leq 0.82 \; \text{M}$ | 1 M                       |

| Output capacitor $[\mu F]$           | *02                           | *(                      | 10                      | 10                        | 10              | 10                      | 4.7                       |

| Flying Capacitor $[\mu F]$           | $2\times2.2$                  | 2.2                     | ı                       | ı                         | $2 \times 0.47$ | $2 \times 260$          | I                         |

| Inductor $[\mu H]$                   | 1(                            | 0                       | 10                      | 10                        | $2 \times 3.3$  | 18                      | 10                        |

| $DCR$ [m $\Omega$ ]                  | 140                           | 350                     | 140                     | 230                       | 166             | ı                       | 75                        |

| Inductor Vol. [mm <sup>3</sup> ]     | $5 \times 4 \times 1.5$       | $2.5 \times 2 \times 1$ | $5 \times 4 \times 1.5$ | $4 \times 3.2 \times 1.2$ | I               | ı                       | $5.2 \times 5.2 \times 3$ |

| Efficiency [%]                       | 91.15 (93.6)                  | 90.33                   | 88                      | 88                        | 93.5            | 89.5                    | 93                        |

| Load @ peak eff.[mA]                 | 30 (50)                       | 25                      | 55                      | 40                        | 100             | 100                     | 100                       |

| $V_{IN} \otimes \text{peak eff.}[V]$ | 3.7 (5)                       | 3.7                     | 3.7                     | 3.7                       | 4.2             | 9                       | 11                        |

| $V_{OUT}$ @ peak eff.[V]             | 30 (20)                       | 30                      | 28                      | 28                        | 18.9            | 30                      | 28.8                      |

| Control                              | Volt                          | Voltage                 | Current                 | Current                   | Voltage         | External                | Current                   |

| Active area $[mm^2]$                 | 2.76                          | 92                      | 3.95                    | 2.27                      | 0.89            | 8                       | T                         |

\*Unfortunately, a larger capacitor was used due to an oversight/error during the PCB design. There is no degradation in efficiency in using a smaller output capacitor.

Figure 2.28: Measured efficiencies at different input and output voltages.

Figure 2.24 shows the small-signal ripple on the  $V_{OUT}$  and  $V_{MID}$  nodes. The expected shapes of ripple on  $V_{MID}$  and  $V_{OUT}$ , as explained in Sec. 2.3 E, proves the effectiveness of the time-interleaving approach to avoid large ripple on the output voltage. Even though  $V_{MID}$  experiences large voltage jumps ( $\sim 200 \text{ mV}$  at  $I_{LED} = 25 \text{ mA}$ ) caused by the flying capacitors exchanging positions, thanks to interleaving of the SC-stage, output voltage ripple remains less than 20 mV. Figure 2.25 shows the start-up transients for  $V_{OUT}$ ,  $V_{MID}$  and inductor current  $I_{IND}$ . Figure 2.27 shows a full-load step of 0-100 mA causing about a 1 V droop. This is primarily because of the lowbandwidth voltage-mode control loop. Efficiency over a load current range of 0.5 mA-100 mA was measured under different  $V_{IN}$ ,  $V_{OUT}$ , and the results are plotted in Fig. 2.28. These results were obtained by using a 504015 casing  $(5.0 \text{ mmx} 4.0 \text{ mmx} 1.5 \text{ mm}) 10 \mu H \text{ inductor (DCR} = 140 \text{ m}\Omega)$ . Efficiency curves plotted with  $V_{OUT}=30~\mathrm{V}$  and  $V_{IN}=2.5~\mathrm{V},\,3.7~\mathrm{V}$  and 5 V show peak efficiency of 91.15% at  $V_{IN} = 3.7 \text{ V}/I_{LED} = 30 \text{ mA}$  and 92.42% at  $V_{IN} = 5$  $V/I_{LED} = 45$  mA. The converter is functional at  $V_{IN} = 2.5$  V to guarantee overall system functionality even when the battery is almost fully discharged. Efficiency curves measured across three temperatures ( $0^{\circ}C$ ,  $25^{\circ}C$  and  $85^{\circ}C$ ),

Figure 2.29: Measured efficiencies with different temperature and external inductance at  $V_{IN}$ =3.7 V and  $V_{OUT}$ =30 V.

Figure 2.30: DCM efficiency at loads less than 5 mA.

shown in Fig. 2.29, indicate efficiency degrades by less than 2% across the temperature range.

Peak efficiency greater than 90% at  $I_{LED} = 30mA$  was obtained even when a smaller volume inductor (25201 casing with DCR = 350 m $\Omega$ ) is used (see Fig. 2.29). The efficiency in DCM- and CCM-modes is shown in Fig. 2.30. Efficiency is improved by 10% at 1 mA load current in the DCM mode, thus proving the effectiveness of the zero-current detector. Summary of the achieved performance and comparison with state-of-the-art high efficiency LED drivers is shown in Table 2.2. This work achieves more than 3% efficiency improvement compared to [33], [7] which have comparable input and output voltages. Compared to [14], the proposed converter's output voltage is 1.7x larger and doesn't require an extra inductor. In an attempt to have some comparison data, we measured the performance of our converter at  $V_{IN}/V_{OUT}$  of 5 V/20 V and 50 mA load current. The peak efficiency was 93.6% when using the 140 m $\Omega$  10  $\mu$ H inductor. It is difficult to fairly compare this work with [14] because of the differences in the conversion gain (4.5 versus 10), output voltage (20 V versus 35 V), load current (100 mA versus 25 mA), switch ratings (10 V versus 20 V). However, comparing [14] and this work at a conversion gain of 4.5 and load current of 25 mA (after downscaling the losses reported at 100 mA in [14] and keeping the area equal) shows that the total losses in this works are 18\% less compared to [14].

# 2.6 Conclusion

We presented a new hybrid boost converter architecture for improving the efficiency of LED drivers used in mobile applications. By cascading a low-switching frequency time-interleaved series-parallel SC-stage with an inductive boost converter, we demonstrated that switching losses can be greatly reduced. Charge-sharing losses of the SC stage are minimized by soft-charging flying capacitors with the inductor of the boost stage. Fabricated in 180 nm BCD process, the prototype converter generates 30 V output voltage from a Li-ion battery source and can provide a load current in the range of 0 to 100 mA with an excellent peak power efficiency of 91.15% at 30 mA. Compared to state-of-the-art designs, the proposed converter achieves a 3% improvement in peak power efficiency.

# CHAPTER 3

# A 1% LINEAR DUTY-CYCLE SENSOR FOR CURRENT SENSING APPLICATIONS IN BUCK CONVERTERS

#### 3.1 Introduction

Current sensing in DC-DC power converters is required for several reasons. Most common applications include filter based inductor-current sensor used in current mode control schemes [34],[3]. Embedded software of portable devices such as mobile phones and tablets, need the DC load current information to optimise their operation, enhancing battery life [35] [2]. Such optimisations include reducing system clock frequency, shutting down modules not required by the currently operations and estimating available battery life for portable devices. Output current sensing is needed in over-current detection modules which protect the DC-DC converter and the PCB from excessive currents [36]. Even though the sensing accuracy requirement is driven by the application, higher accuracy leads to lesser overhead in design. For instance, a 10 A over-current sensor with 20% inaccuracy can trip anywhere between 8 A and 12 A. For applications requiring 8 A current limit, the system must handle up-to 12 A resulting in significant overhead in design.

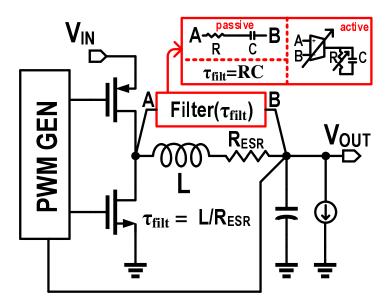

Reported current-sensing schemes can be broadly divided into two categories: filter-based and current-mirror based approaches. The filter based approach, primarily used in current-mode control schemes, essentially emulates the inductor-ESR time constant with an RC-filter placed in parallel with the inductor as shown in Fig. 3.1 [34]. The time-constant matching requirement, makes this approach very sensitive to temperature variation and manufacturing tolerances of passive components, resulting in a large sensing error of  $\pm 25\%$ . Replacing the passive filter with an active filter and calibrating its time constant leads to a reduced error of  $\pm 18\%$  [37], but remains sensitive to inductor variation across the load range.

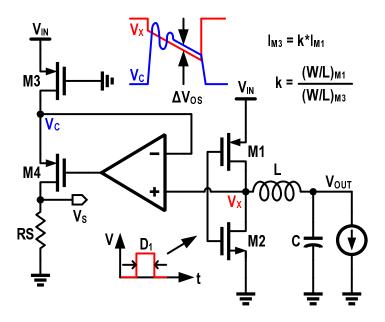

The current-mirror based approach produces a scaled copy of the current

Figure 3.1: Filter-based current sensing.

through the high-side (or low-side) FET, M1, using a replica FET, M3, as shown in Fig. 3.2. This approach achieves a better performance of  $\pm 4\%$  [38][39]. It is primarily limited by matching errors in the replica MOSFET and offset and settling errors in the amplifier used for matching drain voltages for both the main and the replica MOSFETs.

Figure 3.2: Replica current based current-sensing.

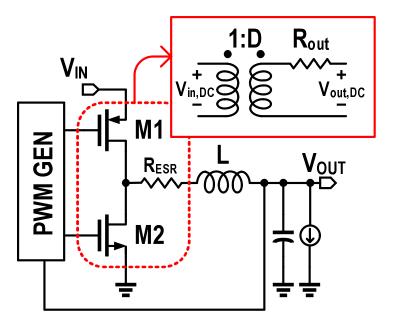

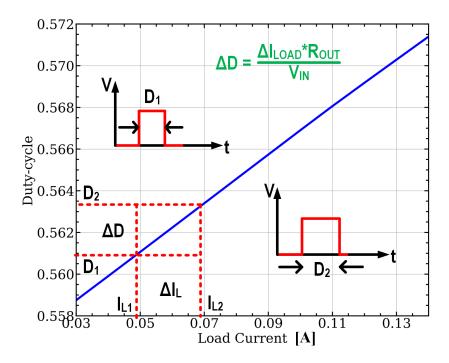

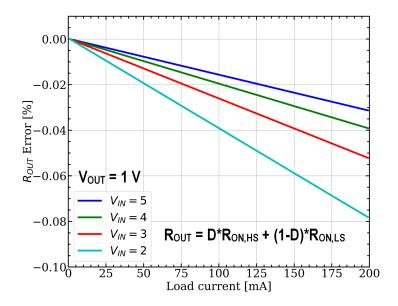

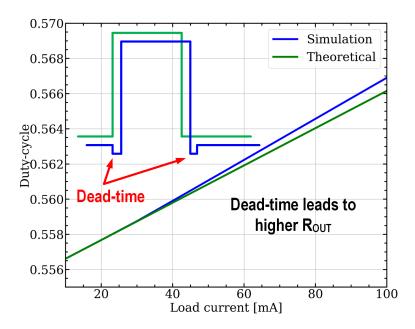

We observe that the duty-cycle of a well-regulated DC-DC power converter