## TOWARDS SCALABLE AND SPECIALIZED APPLICATION ERROR ANALYSIS

## BY

## ABDULRAHMAN HASSAN N MAHMOUD

#### DISSERTATION

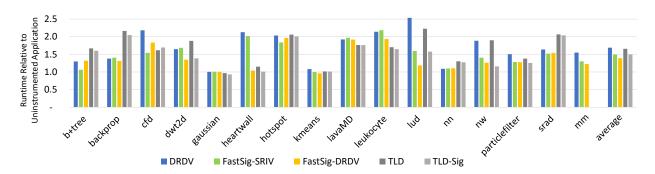

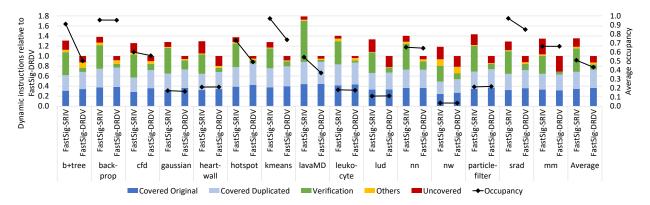

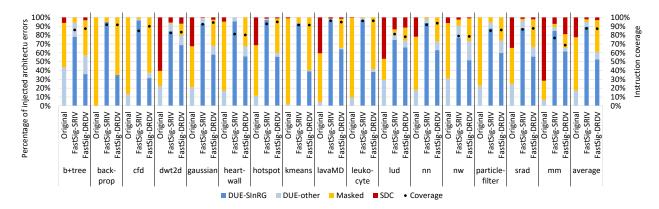

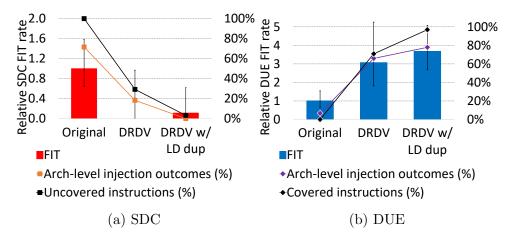

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2020

## Urbana, Illinois

## Doctoral Committee:

Professor Sarita V. Adve, Chair & Director of Research Professor Darko Marinov

Assistant Professor Christopher W. Fletcher

Assistant Professor Sasa Misailovic Dr. Siva Kumar Sastry Hari, NVIDIA

Professor Luis Ceze, University of Washington

#### Abstract

Modern systems at scale are increasingly susceptible to transient hardware errors at current technology sizes from natural phenomena such as high-energy particle strikes (also called soft errors). Traditional solutions aimed at dealing with soft errors, however, typically rely on indiscriminate redundancy in space and/or time for resilience. Such techniques can incur high system overheads, whether in manufacturing cost, runtime performance, energy consumption, and/or area requirements. Moreover, the all-or-nothing protection offered by full redundancy may result in over-protection and inefficient use of resources. To that end, while it is critical to be able to protect against the effect of hardware errors, it is important to do so in an an efficient and low-cost manner.

One way to reduce the cost of protecting applications from hardware errors is to understand *how* errors propagate at finer granularities, and only protect vulnerable components via selective duplication. This raises three important questions:

- 1. What granularity of analysis is reasonable to target?

- 2. Which components at this granularity should be selected for protection?

- 3. How should the selective protection be implemented in a low-cost manner?

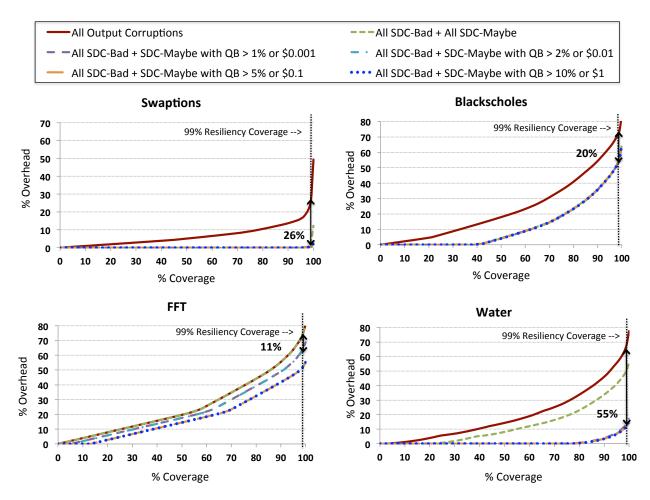

This thesis addresses these three questions with the design of multiple tools and techniques geared towards identifying and understanding how single-bit flip errors propagate and affect an application's output. First, we present a general-purpose tool called Approxilyzer. Approxilyzer uses the novel error pruning and equalization techniques pioneered by a prior tool, Relyzer, to quantify the impact of virtually every error site in an application. Targeting the instruction-level granularity for analysis and protection, Approxilyzer shows that not all errors are equally important, and that trading off a small output quality degradation (for example, 1%) can yield large resiliency overhead reduction (up to 55%) for 99% resiliency coverage.

While Approxilyzer is a promising tool for resiliency analysis, it initially took a long time to run due to the large number of error sites requiring exploration in an application. To accelerate error analysis tools (such as Approxilyzer), the second part of this thesis introduces a software-testing inspired toolkit called Minotaur. Minotaur bridges the gap between software testing and hardware resiliency by adapting multiple techniques from the software engineering domain to make hardware error analysis faster and thus more scalable.

We show that Minotaur can significantly improve the runtime of Approxilyzer ( $10.3 \times$  on average), while *simultaneously* improving its accuracy in identifying vulnerable instructions which need protection.

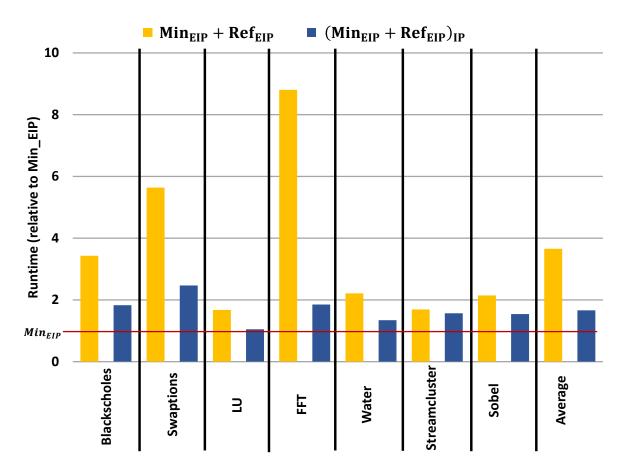

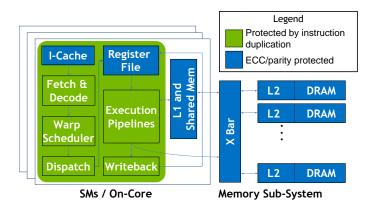

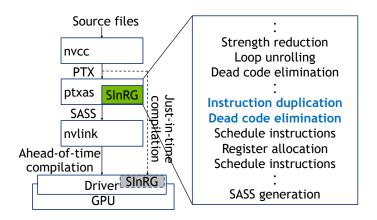

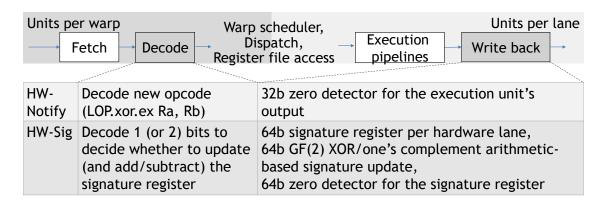

The third part of this thesis focuses on reducing the implementation overhead of instruction-level duplication, by taking into consideration the hardware platform and unique opportunities provided by the backend architecture. Specifically, we develop a tool called SInRG, or Software-managed Instruction Replication for GPUs. SInRG provides a family of instruction duplication techniques that exploit underutilized hardware resources for error detection. Inspired by CPU instruction-level duplication, SInRG establishes the first practical approach to software-directed instruction duplication for GPU-based systems, identifies GPU-specific opportunities for overhead reduction, and explores software and hardware performance optimizations to lower the overheads of replication significantly. The GPU-specific software optimizations trade off error containment for performance and reduce the average runtime overhead to 36%. We also propose new ISA extensions with limited hardware changes and area costs to further lower the average runtime overhead to just 30%.

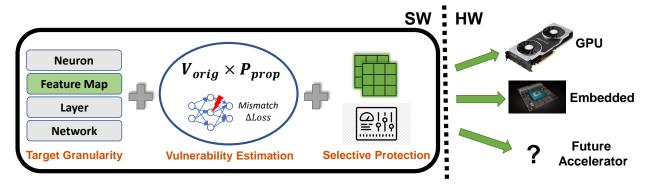

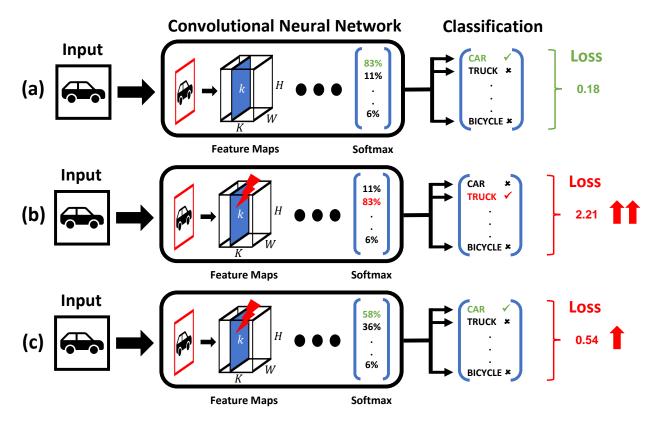

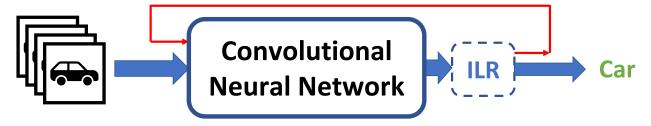

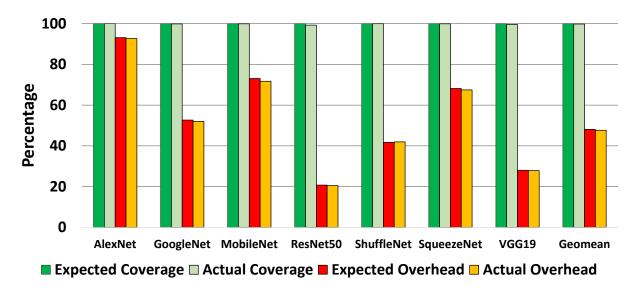

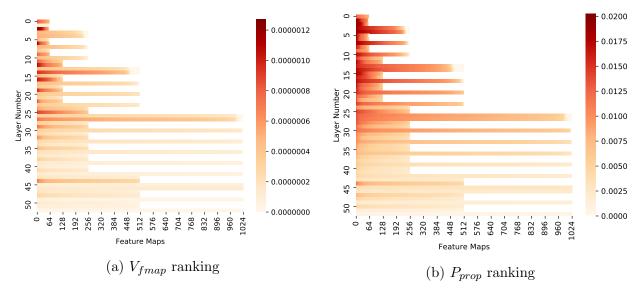

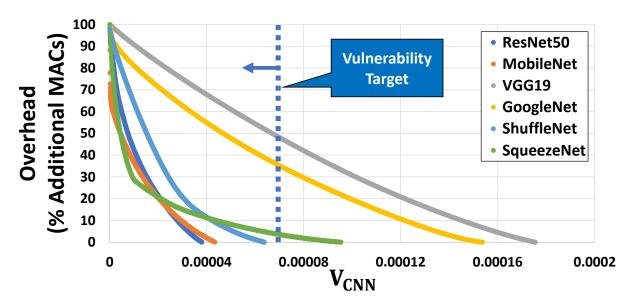

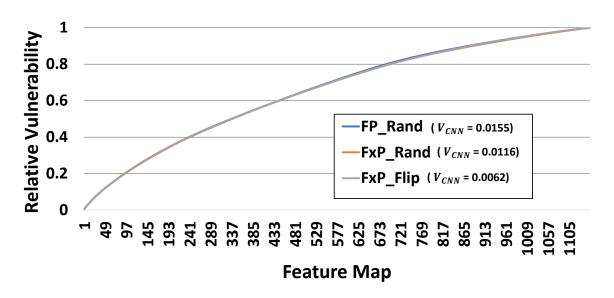

General purpose error analysis and hardening techniques provide the benefit of being universally applicable to general purpose code. Given additional information about the application, however, can further enable low-cost resiliency solutions by leveraging domain knowledge. The fourth part of this thesis uses this premise to perform a *specialized* resiliency analysis for convolutional neural networks (CNNs), due to their prevalence in many safety-critical application such as self-driving cars. We develop and evaluate two selective protection techniques at different target granularities in CNNs (feature map level and inference level), and show that the combination of both techniques is better than the sum of its parts. Our results show that the specialized, domain-specific error analysis and hardening techniques can achieve very high error coverage of 99.78% on average for the CNNs explored, while incurring as low as 20% overhead, or  $5 \times$  less overhead compared to full duplication.

Overall, this thesis focuses on understanding *how* hardware errors propagate to corrupt an application's output. We develop multiple tools and techniques for error analysis, and advocate for specialized, selective protection solutions as a means to achieve low overheads while maintaining high error coverage in applications.

## Acknowledgments

This Ph.D. journey would not have been possible without the help of so many people along the way. Most of all, I need to thank my advisor, Dr. Sarita Adve, for all her kindness, patience, dedication, and support throughout this process. I have learned so much during this time having worked with her, and I have become a much better researcher and person as a result. Thank you, Sarita, for everything you have taught me and coached me over the years.

Many parts of this thesis were done in collaboration with Dr. Siva Hari. Besides being an excellent researcher, collaborator and mentor, Siva is one of the kindest and most genuine people I have ever met. I am lucky to have worked with him on multiple projects, and even more fortunate to have gotten to know him and benefit from his great mentoring.

I also sincerely appreciate all the feedback and interactions from the rest of my Ph.D. committee. Dr. Darko Marinov, thank you for providing me a quote for the ages: "Be with the force. Read the source." Dr. Chris Fletcher, your enthusiasm and passion are contagious, and I always look forward to our many chats. Dr. Sasa Misailovic, my results are finally here, put together in thesis form. Dr. Luis Ceze, thank you for always having time for me, and constantly providing positive feedback and encouragement.

The entire Computer Science department staff at Illinois is incredible. Thank you for all the assistance throughout, and for making the time I spent here during my Ph.D. very enjoyable and conducive to success. Special thanks to Kim Baker, Jennifer Dickens, Dana Garard, Samantha Hendon, Joe Jeffries, Mary Beth Kelly, Viveka Kudaligama, Kara Mac-Gregor, Rhonda McElroy, Maggie Metzger Chappell, Michelle Osbourne, Colin Robertson, Kathy Ann Runck, and Glen Rundblom. Any success I have had is a tribute to their incredible efforts along the way.

My work has been supported by the National Science Foundation under grants CCF 13-20941 and CCF 19-56374, by the Center for Future Architectures Research (C-FAR), one of the six centers of STARnet, a Semiconductor Research Corporation (SRC) program sponsored by Microelectronics Advanced Research Corporation (MARCO) and Defense Advanced Research Projects Agency (DARPA), and by the Applications Driving Architectures (ADA) Research Center, a Joint University Microelectronics Program (JUMP) Center co-sponsored by SRC and DARPA. A portion of this work was performed while I interned at NVIDIA.

I am very thankful to all my collaborators and/or labmates: Neeraj Aggarwal, Khalique Ahmed, Dr. John Alsop, Wesley Darvin, Dr. Iuri Frosio, Aditi Ghosalkar, Sam Grayson, Dr.

Steve Keckler, Alex Nobbe, Dr. Pavlo Molchanov, Paul Reckamp, Charbel Sakr, Giordano Salvador, Dr. Naresh Shanbhag, Dr. Matthew Sinclair, Rahul Singh, Dr. Michael Sullivan, Phoebe Tang, Dr. Timothy Tsai, and Dr. Radha Venkatagiri.

I would like to particularly thank Radha for all her work and collaboration together throughout the years. Her encouraging spirit and approachable nature have made bouncing ideas off of one another and working together an enjoyable and enlightening experience!

Special thanks to Muhammad Huzaifa. An amazing friend, buddy, teammate, collaborator, soccer player, motorcycle enthusiast, and generally a great person to be around. You have made this ride very enjoyable my friend.

Finally, a very special thank you to my wife, Hanan, for all her love and support throughout. You have always been my number one fan, my pillar of support, and my better half. To my son, Musa, you helped make this journey more exciting than it ever could have been, and your smile and laugh are my favorite things in the whole wide world. To my loving family and community: thank you for always being there for me, and carrying me to the finish line.

# **Table of Contents**

| Chapter 1 Introduction                                                    |      | <br>1  |

|---------------------------------------------------------------------------|------|--------|

| 1.1 Motivation                                                            |      | <br>1  |

| 1.2 Summary of Contributions                                              |      | 3      |

| 1.3 Thesis Organization                                                   |      | <br>6  |

| Chapter 2 Principled and General Purpose Hardware Error Analysis          |      | <br>8  |

| 2.1 Motivation                                                            |      | 8      |

| 2.2 Background: Principled Error Pruning Techniques                       |      | 10     |

| 2.3 Approxilyzer: A Framework for Instruction-Level Error Analysis        |      | 12     |

| 2.4 Evaluation Methodology                                                |      | 18     |

| 2.5 Results                                                               |      | 22     |

| 2.6 Extending Error Analysis to Other Instruction Set Architectures       |      | 32     |

| 2.7 Summary                                                               |      | 41     |

|                                                                           |      |        |

| Chapter 3 Scalable General Purpose Hardware Error Analysis                |      | <br>42 |

| 3.1 Motivation                                                            |      | <br>42 |

| 3.2 Background: Software Testing Techniques                               |      | <br>43 |

| 3.3 Minotaur: Adapting Software Testing Techniques for Hardware Erro      | ors  | <br>44 |

| 3.4 Evaluation Methodology                                                |      | <br>49 |

| 3.5 Results                                                               |      | <br>53 |

| 3.6 Minotaur Extensions                                                   |      | <br>62 |

| 3.7 Summary                                                               |      | <br>64 |

| Chapter 4 Optimizing General-Purpose, Software-Directed Instruction-Level | Pro- |        |

| tection                                                                   |      | <br>65 |

| 4.1 Motivation                                                            |      | <br>65 |

| 4.2 Background and Challenges                                             |      | <br>67 |

| 4.3 SInRG: Software-Managed Instruction Replication for GPUs              |      | 68     |

| 4.4 SInRG Implementation                                                  |      | 72     |

| 4.5 Evaluation Methodology                                                |      | <br>78 |

| 4.6 Results                                                               |      | 81     |

| 4.7 Summary                                                               |      | 87     |

| Chapter 5 PyTorchFI: A Runtime Perturbation Tool for DNNs                 |      | 88     |

| 5.1 Motivation                                                            |      | 88     |

| 5.2 Background                                                            |      | 89     |

| 5.3 Tool Description                                                      |      | 90     |

| 5.4 PyTorchFI Use Cases                                                   |      | 94     |

| 5.5 Summary                                                               |      | 99     |

| Chapter   | 6 Domain-Specific Resiliency Analysis Techniques for Deep Learning 10 | 1 |

|-----------|-----------------------------------------------------------------------|---|

| 6.1       | Motivation                                                            | 1 |

| 6.2       | CNN Error Model                                                       | 3 |

| 6.3       | FLR: Feature-Map Level Resilience                                     | 3 |

| 6.4       | ILR: Inference Level Resilience                                       | 8 |

| 6.5       | FILR: ILR + FLR                                                       | 0 |

| 6.6       | Evaluation Methodology                                                | 0 |

| 6.7       | Results for Effectiveness of Techniques                               | 3 |

| 6.8       | Detailed Analysis and Extensions                                      | 2 |

| 6.9       | Summary                                                               | 0 |

| Chapter   | 7 Related Work                                                        | 2 |

| 7.1       | General Purpose Resiliency                                            | 2 |

| 7.2       | Approximate Computing                                                 | 3 |

| 7.3       | GPU Resiliency                                                        | 5 |

| 7.4       | CNN Resiliency                                                        | 6 |

| Chapter   | 8 Conclusion and Future Work                                          | 8 |

| 8.1       | Conclusions                                                           | 8 |

| 8.2       | Limitations and Future Directions                                     | 9 |

| Deference | 1.4                                                                   | 1 |

## **Chapter 1: Introduction**

#### 1.1 MOTIVATION

As we approach the end of conventional transistor scaling, hardware is becoming increasingly susceptible to errors in the field [1, 2, 3, 4, 5, 6]. Commodity hardware is used in systems with a range of reliability requirements, from entertainment devices such as personal phones to stringently safety-critical systems such as self-driving cars. Modern systems at scale are especially susceptible to transient hardware errors (also called *soft errors*) at current technology sizes from natural phenomena such as high-energy particle strikes, wear out, and/or voltage droops [3, 7, 8]. With exascale systems scaling to hundreds of thousands of nodes, automated driving systems on the roads, and wearable medical devices increasing in use, it is critical to protect against the increased likelihood of hardware events causing system errors and/or crashes.

Studies have shown that hardware errors can have severe unintended consequences unless the system is designed to detect these errors [9, 10]. Many high-performance computing (HPC) field studies [11, 12, 13] and exascale reports and challenges [3, 7, 8] assert the importance of designing error-tolerant systems. Traditional reliability solutions, however, typically rely on full and indiscriminate redundancy in hardware or software to ensure high resilience. This can be both costly and inefficient at the system level. Although it is crucial to detect hardware errors in such systems to ensure high reliability guarantees, hardware errors themselves occur infrequently such that full, indiscriminate redundancy may be overkill for many systems.

Early work recognized that a large majority of hardware errors are either masked at the software level (i.e., they did not change the output of the executing program) or result in easily detectable anomalous software behavior (e.g., exceptions due to unaligned or out-of-bounds addresses) [14, 15, 16, 17, 18, 19, 20]. The former errors require no action and the latter can be detected using zero to very low-cost detection mechanisms. While such software-centric resiliency techniques show immense promise, unfortunately, some hardware errors escape detection and result in undetected and potentially unacceptable silent data corruptions (SDCs) of the program output.

SDCs have been an obstacle in the widespread adoption of software-centric resiliency techniques; therefore, significant recent research has focused on characterizing and reducing these SDCs either through hardware solutions (e.g., use of error-correcting code, or ECC, in hardware memory structures) or software solutions (e.g., insertion of software checks and

assertions in application code regions determined to be too vulnerable to SDCs) [19, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32].

Underlying all of these solutions is the need for techniques that find SDCs in the applications of interest. Software resiliency (or just resiliency) is the ability of a given piece of software to avoid an SDC for a given hardware error, and can be divided into two primary components. The first component is resiliency analysis, which involves characterizing the resiliency of a given piece of software for a given set of hardware errors. The second component is resiliency hardening, whereby either software or hardware modifications are made to make the software more resilient. Each component offers unique research challenges in the identification and mitigation of SDCs.

In order to avoid the heavy hammer of indiscriminate redundancy for software resilience, a developer can perform an offline analysis of the workload to help pinpoint vulnerabilities before deployment in the field. The primary drawback of such a resiliency analysis, however, is that the number of potential error sites requiring exploration can be extremely large. For example, assuming a single-bit flip error model in an application would require studying the impact of every bit flip of every register of every dynamic instruction in the application – clearly an intractable proposition.

Prior work in resiliency analysis imposes a significant trade-off between speed and accuracy. Statistical analyses based on dynamic error-free execution traces or static code [27, 33, 34, 35, 36] are unable to precisely model error propagation paths. Randomized error injection campaigns [37, 38, 39, 40, 41] can only provide statistical information and are unable to predict resilience for code portions where errors were not injected. More systematic and comprehensive error-injection techniques [42, 43] can precisely identify SDC-causing instructions but are much slower than the previous techniques.

Resiliency analysis can have a direct (positive) influence on hardening overheads, by reducing the amount of work required by hardening techniques to only the vulnerable error sites from the analysis. Resiliency hardening however, does not need to solely depend on an offline analysis: various software-hardware co-designed protection techniques can be employed which operate in an "always-on" mode. Such a hardening solution instead depends on understanding the hardware platform running the code, and exploiting spare resources to "hide" protection overheads effectively. While such a technique can be beneficial for some workloads, combined with an offline analysis can make it even more powerful as a low-cost deployment resilience solution.

While the aforementioned analysis and hardening techniques can be universally applicable to general-purpose code, a general purpose approach which does not take into consideration the executing workload may perform sub-optimally in terms of minimizing the cost of resilience while ensuring high-error coverage. Instead, by tuning resiliency to the application, we can further reduce resiliency overheads. Major challenges involved in such an endeavor include understanding how errors propagate in the application, and crafting solutions that guard against the most egregious output corruptions.

This thesis aims to address many of the challenges described above by introducing tools and techniques that help understand how hardware errors propagate, and how to mitigate such errors using low-cost protection mechanisms. This thesis argues for scalable and specialized application error analysis tools to enable low-cost hardening techniques. Further, given the recent meteoric rise of machine learning and deep learning in many safety-critical applications, this thesis performs a deep-dive into convolutional neural network (CNN) resilience. Overall, we show that software-directed resiliency techniques not only have high SDC detection capabilities, but can also do so with lower overheads than traditional mechanisms.

#### 1.2 SUMMARY OF CONTRIBUTIONS

To address the challenges involved in identifying and protecting against hardware errors, it is important to categorize and understand how errors propagate at various granularities in a system. Moreover, it is critical to design tools and techniques which capitalize on the gathered insights and understandings, while simultaneously ensuring the usability of such tools in terms of their performance and accuracy. The following sections summarize the contributions made in this thesis.

All the following work has been a collaborative effort, with shared contribution among fellow students, faculty, and industry researchers.<sup>1</sup> Radha Venkatagiri is the lead author on the Approxilyzer tool described in Chapter 2. Khalique Ahmed led the effort in the gem5-Approxilyzer work described in Section 2.6. I co-led the work described in Chapter 3 with Radha. I am the lead author of the work described in Chapters 4, 5, and 6.

#### 1.2.1 Principled and General Purpose Error Analysis Techniques

Despite the fact that errors carry a negative connotation, not all errors are created equal. While some errors are egregious and must be identified and mitigated, other errors are tolerable and may have little or no impact on the system or application. In order to identify which errors are "bad" and must guarded against while dismissing errors which are "good"

<sup>&</sup>lt;sup>1</sup>Chapters 2 – 6 are heavily based on the publications I led and co-led.

and can be tolerated, it is necessary to understand how errors propagate once a fault manifests in the hardware. This requires *principled* and comprehensive tools to perform such an analysis.

One challenge these tools must overcome is the extremely large space of possible errors, given an error model. For example, if we assume an alpha particle strike can flip a random bit of a register during program execution, the plurality of errors would include studying the impact of every bit flip of every register of every dynamic instruction for a running application. This is prohibitively expensive.

In addition to reducing the error space, we also need to understand the impact an error has on the *quality* of an application's output, an important contribution of this thesis. This type of analysis can significantly help in reducing the typically high overhead associated with reliability. Further, it can help in identifying which errors are especially important to protect and which can be dismissed due to their low impact on the application's output quality.

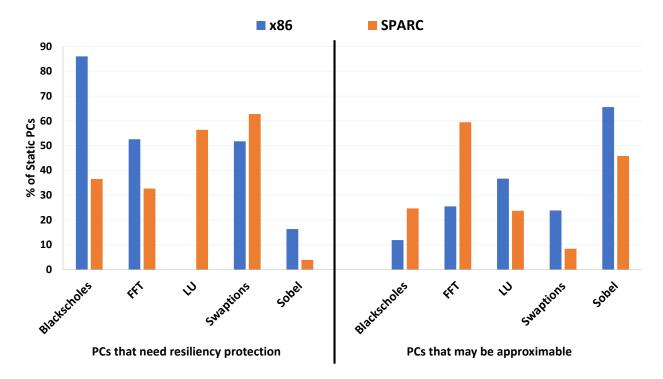

To address these issues, the first contribution of this thesis is the development of Approxilyzer [44] and gem5-Approxilyzer [45]. Using the novel error-site pruning techniques pioneered by Relyzer [42], Approxilyzer quantifies the quality impact of a single-bit error in all dynamic instructions of an execution with high accuracy. We demonstrate two uses of Approxilyzer. First, we show how Approxilyzer can be used to quantitatively tune output quality versus resiliency versus overhead to enable ultra-low cost resiliency solutions (for a single bit flip error model). For example, we show that Approxilyzer determines that a very small loss in output quality (1%) can yield large resiliency overhead reduction (up to 55%) for 99% resiliency coverage. Second, we show how Approxilyzer can be used to provide a first-order estimate of the approximation potential of general-purpose programs. It does so in an automated fashion while requiring minimal user input and no program modifications. We extend Approxilyzer to gem5-Approxilyzer, an open-source implementation that enables support for various instruction set architectures (ISAs); we study the error profile of applications in the x86 and Scalable Processor Architecture (SPARC) ISAs for comparison. Effectively, Approxilyzer is a comprehensive, general-purpose tool which provides instruction-level error analysis with quality assessment.

#### 1.2.2 Scaling Up Error Analyses Through Software Testing Techniques

Even with principled analysis, the space of possible errors may still be very large, and a comprehensive analysis can still be slow. To promote the adoption of highly effective error analysis tools such as Approxilyzer, an underlying requirement is that the tool must be fast, without sacrificing accuracy of error analysis. To address this challenge, the second contribution of this thesis is to leverage the extensive line of work from the domain of software testing, and adapt it to hardware resiliency. The novel insight here is that analyzing software for resiliency to hardware errors is similar to testing software for software bugs; therefore, adapting techniques from the rich software testing literature can substantially improve the state-of-the-art in resiliency analysis.

The result is called Minotaur [46], a software testing inspired toolkit which can accelerate error analysis tools such as Approxilyzer. Minotaur bridges between software testing and hardware reliability by adapting four software testing techniques to make hardware error analysis faster and thus more scalable. As a result, we show that Minotaur improves the runtime of Approxilyzer by an order of magnitude  $(10.3\times)$  on average while *simultaneously* improving the accuracy of Approxilyzer in identifying hardware errors.

### 1.2.3 Optimizing General Purpose Protection Through Software-Managed Techniques

Error analysis forms only part of the equation when it comes to making application resilient in the face of hardware errors. Another important aspect involves hardening the application to avoid errors at runtime. For example, one mechanism for hardening an application is duplicating all vulnerable instructions in order to detect errors and notify the system at runtime. Although advantageous from a resiliency perspective, this can incur significant overheads which may not be acceptable, especially for mission critical applications with real-time constraints.

To study the implementation overhead of instruction-level duplication, the third contribution of this thesis is the development of a tool called SInRG [47], or Software-managed Instruction Replication for GPUs. SInRG provides a family of instruction duplication techniques that exploit underutilized hardware resources for duplication. This work describes a practical methodology to employ instruction duplication for graphics processing units (GPUs) and identifies implementation challenges that can incur high overheads (69% on average). It explores GPU-specific software optimizations that trade fine-grained recoverability for performance. It also proposes simple ISA extensions with limited hardware changes and area costs to further improve performance, cutting the runtime overheads by more than half to an average of 30%.

We find that the optimal SInRG duplication strategy is workload dependent: based on the hardware resource utilization of the workload, a particular SInRG techniques performed better or worse. For example, a workload with heavy register utilization would benefit from a duplication strategy that avoids increasing register pressure. Thus, by leveraging applicationspecific information, developers can potentially design lower-cost resiliency solutions.

## 1.2.4 Specialized, Application-Driven Reliability for CNNs

The fourth contribution of this thesis is an end-to-end, specialized reliability toolset for CNN workloads. As CNNs become more prevalent in safety-critical applications such as self-driving vehicles, it is imperative that they behave reliably in the face of hardware errors. Thus, rather than relying on general purpose tools for analysis and protection, we ask the question: can we leverage domain-specific knowledge for resiliency analysis and hardening?

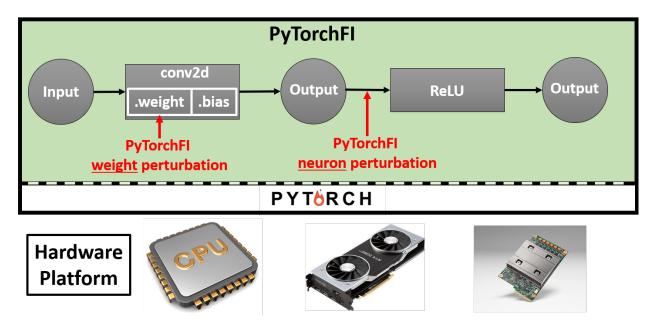

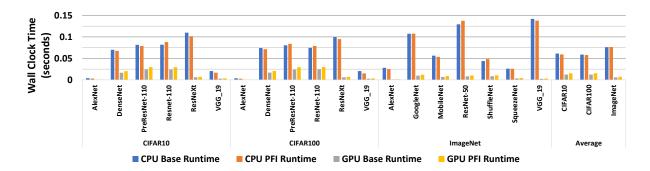

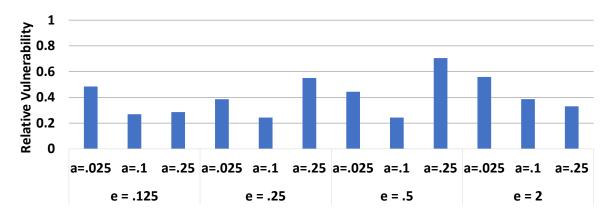

We develop and open-source a tool called PyTorchFI [48], which allows us to study the impact of transient errors on the outcome of a CNN inference. Using PyTorchFI, we introduce two software-driven, selective protection techniques that target different protection granularities of a CNN. First, we develop a feature map level resilience technique (FLR) [49], which identifies and statically protects the most vulnerable feature maps in a CNN. Second, we develop an inference level resilience technique (ILR), which selectively reruns vulnerable inferences by analyzing their output. Finally, we show that the combination of both techniques (called FILR) is highly efficient. Our results show that the combination can achieve very high error coverage of 99.78%, while incurring only 48% overhead on average (and as low as 20% for ResNet50, or 5× less overhead compared to full duplication).

#### 1.3 THESIS ORGANIZATION

This thesis is organized as follows. Chapter 2 introduces Approxilyzer and gem5-Approxilyzer, two general-purpose hardware error analysis tools that quantitatively measure the impact of errors at the instruction-level. While Approxilyzer and gem5-Approxilyzer can attain orders-of-magnitude gains via error pruning and equalization of errors (leveraging Relyzer techniques), these tools can still take a long time to complete the analysis. To address this issue, Chapter 3 proposes and evaluates the toolset Minotaur, showing how employing and adapting software testing techniques to the field of hardware error analysis can dramatically speed up application error analysis without loss of accuracy. Next, Chapter 4 presents SInRG, a family of low-cost, instruction-level duplication techniques which leverage spare hardware resources to effectively hide error detection overheads in general-purpose code.

Our results in Chapters 2–4 show that incorporating information about an application can help optimize resiliency analysis and hardening techniques. Chapter 5 introduces PyTorchFI, a specialized runtime perturbation tool for deep learning. Using PyTorchFI, Chapter 6 introduces and promotes a fully application-based error analysis and detection approach for CNNs. Chapter 6 explores different granularities of analysis and protection for software-

directed error analysis of CNNs, and shows that a combination of techniques at different granularities is better than the sum of its parts. Chapter 7 highlights related work, and Chapter 8 summarizes the contributions of this thesis and discusses potential future research directions.

## Chapter 2: Principled and General Purpose Hardware Error Analysis

#### 2.1 MOTIVATION

Traditional solutions for dealing with hardware errors in the field have relied on indiscriminate redundancy in space and/or time [50, 51, 52, 53]. For example, Tesla released a Full Self Driving (FSD) system in March 2019 which deploys two fully redundant FSD chips along with accompanying redundant control logic, power, and peripheral packaging on the board for reliability [53]. This solution of indiscriminate redundancy, however, is in direct tension with a key implication of the end of the Moore's Law and Dennards scaling era: hardware designers are now severely constrained by power and area, and must obtain improved efficiency to stay on the performance and functionality curves to enable future applications [54]. Indiscriminate redundancy incurs too much overhead in cost, area, power, and/or performance for most systems [1, 27, 30, 36, 55, 56, 57, 58, 59, 60]. This overhead is particularly onerous since in many cases, it unnecessarily overprotects against hardware errors.

A promising alternative to full application redundancy is the use of software for the detection for hardware errors. Software-centric solutions aim to identify anomalous software behavior due to hardware errors with the use of low-cost techniques [14, 15, 16, 17, 18, 19, 20, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32]. However, many hardware errors still manage to escape detection, resulting in unacceptable silent data corruptions, or SDCs, of the program output [30, 61, 62, 63]. Therefore, significant research has focused on analyzing these SDCs, and reducing them through either hardware or software solutions.

Resiliency analysis techniques used in practice to help uncover SDCs can generally be categorized into two major categories: experimental error injection campaigns or analytical error propagation models. An experimental error injection campaign involves performing many error injection experiments, each of which emulates a hardware error by perturbing internal program state, and then executing the program to completion to evaluate the effect of the error [64, 65, 66]. Since a program can consist of trillions of operations and there are a plurality of errors possible for each operation, a primary challenge of this approach is the large amount of time and resources needed to completely characterize the resilience of an application. On the other hand, analytical error propagation models attempt to reduce the resource intensity of error injection by estimating the vulnerability of different operations through higher-level models that take into account architecture or domain knowledge [67, 68, 69]. Section 7 goes into more detail on specific resiliency analysis techniques from the

literature.

In order to obtain the accuracy obtained from experimental error injection while avoiding the associated overhead involved, we need to systematically address the large error space and reduce it in a *principled* manner. Furthermore, we need to understand the *impact* an error has on an application's output quality, to determine whether or not it requires protection. To that end, we developed an open-source tool called Approxilyzer [44, 70].

Approxilyzer builds on a resiliency-driven tool called Relyzer [42] which uses a combination of error injection and program analysis to predict the outcomes of errors, assuming all deviations from the error-free output are unacceptable. Relyzer uses an instruction-level transient single bit error model, and determines outcomes for all such errors in the operand registers of all dynamic instructions. We use error site to refer to a specific bit in a specific operand register in a specific dynamic instruction. Using program analysis and some heuristics, Relyzer identifies error sites that behave similarly in the presence of a single-bit error and groups these together into an equivalence class. It then performs an error injection experiment on just one representative error site (called a pilot) and uses its result to predict the outcome for all the error sites in the equivalence class. Hence, Relyzer is able to predict the resiliency characteristics of virtually all the error sites in the application with relatively few error injection experiments and high accuracy.

Approxilyzer builds upon Relyzer by introducing the notion of quality, determining the quality degradation for each predicted SDC, and applying this information in the areas of low-cost resiliency and approximate computing. It takes as input an unmodified program (with input), a quality metric, and an optional acceptable quality threshold, and produces a comprehensive output quality profile. This profile provides the outcome of a transient single bit error in each error site in an execution. The outcome can be masked (an output is produced and is the same as the golden, error-free output), detected (e.g., a fatal trap was invoked), or an output corruption (an output is produced, but is different from the golden output). For the last case, Approxilyzer further categorizes the output as a detectable data corruption (outputs that are visibly incorrect and could be detected; e.g., a not-a-number or NaN) or a silent data corruption. SDCs are further binned into buckets based on the output quality.

We show two applications of Approxilyzer's output quality profile in this chapter. First, for low-cost resiliency (assuming our error model), we use the observation that error sites that result in SDCs that are binned above an acceptable quality threshold do not need any protection. We show how this observation can be used by the programmer to quantitatively tune output quality versus resiliency versus overhead to enable ultra-low cost resiliency solutions.

Second, for a broader application of approximate computing, we observe that an error site is not amenable to approximation if it produces an outcome that is detected, detectable, or an SDC binned below an acceptable quality threshold. Although our error model is limited, it is reasonable to assume that if even a single bit perturbation produces such an unacceptable outcome, then a stronger perturbation will likely also produce the same, making the error site an unlikely candidate for approximation. Thus, Approxilyzer allows the system or programmer to focus on the remaining error sites (and constituent instructions) as candidates for approximation. These sites may or may not result in acceptable outcomes with stronger perturbations than single bit flips, but they provide a smaller subset for further (and potentially easier) analysis with other tools. This pruning of the space of approximable instructions is particularly valuable since it is completely automated – the only requirement from the programmer is the end-to-end quality metric. Knowledge of a threshold for acceptable quality is beneficial, but it is not necessary and can also be conservative. The more conservative the threshold, the more SDCs are deemed as not approximable (in the limit of no threshold, all SDCs are deemed not approximable). In this way, Approxilyzer enables a first-order, automated estimation of the potential for approximation for any general-purpose program.

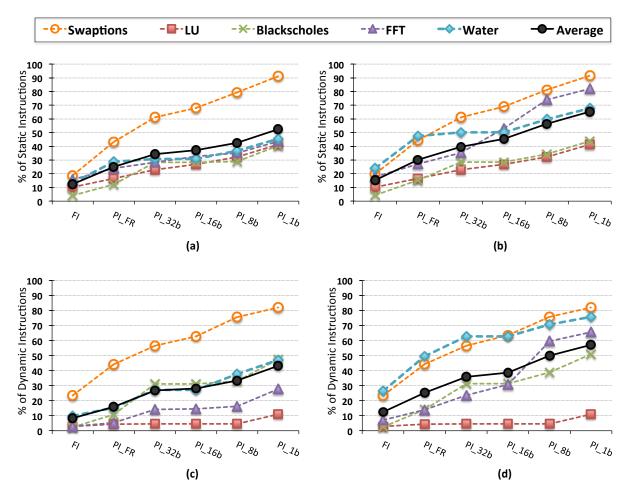

While impactful as a general purpose resiliency tool, Approxilyzer's adoption was limited due to its implementation using the proprietary Simics infrastructure [71] and the SPARC [72] instruction set architecture (ISA). To that end, we also developed and open-sourced gem5-Approxilyzer [45], a re-implementation of Approxilyzer using the open-source gem5 simulator [73]. gem5-Approxilyzer can be extended to different ISAs, starting with x86 in this work. We show that gem5-Approxilyzer is both efficient (up to two orders of magnitude reduction in error injections over a naïve campaign) and accurate (average 92% for our experiments) in predicting the program's output quality in the presence of errors. We also compare the error profiles of five workloads under x86 and SPARC to further motivate the need for a tool like gem5-Approxilyzer.

#### 2.2 BACKGROUND: PRINCIPLED ERROR PRUNING TECHNIQUES

Compared to a naïve campaign that performs an error injection for every error site, principled error pruning can dramatically reduce the number of error injections necessary to predict the error outcome for all error sites. Using the novel heuristics pioneered by Relyzer [42], we leverage two sets of pruning techniques: equivalence-based and known-outcome pruning techniques, which we incorporate for use in Approxilyzer. This section briefly describes these techniques; detailed explanations and examples can be found in prior work [42].

**Equivalence-based** pruning techniques use program analysis (static and dynamic) and heuristics to prune errors that are likely equivalent to others. These techniques partition error sites into *equivalence classes*, where each class requires an error injection into just a single representative error site (called a *pilot*) to predict the error outcome for all other error sites in the class. Approxilyzer implements two equivalence-based pruning techniques: control equivalence and store equivalence.

- Control equivalence groups error sites based on the observation that errors that propagate through similar code sequences are likely to have similar error outcomes. This technique records the next N branches for dynamic instances of a given static instruction in the original execution (with no error injection). Corresponding error sites of dynamic instances that share the same control path (up to depth N) are grouped in an equivalence class.

- Store equivalence is used to equalize dynamic instances of store instructions and instructions that a store depends on within a basic block based on the observation that errors in a store instruction propagate through the loads that read the erroneous value. This technique records the subsequent loads that read from a store address and groups corresponding error sites of dynamic instances of store instructions that have the same list of subsequent loads together.

**Known-outcome** pruning techniques largely use static (and some dynamic) program analyses to determine the outcome of an error. Approxilyzer uses two known-outcome pruning techniques:

- Address-bound pruning uses the observation that single-bit errors that appear outside the address range of an application result in *detected* outcomes. Thus, their outcomes are known a priori and these errors can be pruned.

- **Def-use pruning** uses the observation that an injection in a def is equivalent to an injection in the first use at the same register and bit position, so only one needs to be explored.

By combining all these pruning techniques, error analysis tools can dramatically reduce the total number of error sites that need detailed analysis. Specifically, Relyzer uses these techniques to prune 99.78% of error sites in an application, reducing the number of error sites requiring detailed study by 3 to 5 orders of magnitude. Relyzer uses error injection simulations on the remaining error sites to identify the outcome of errors, and shows 96% validation accuracy on average across all the applications studied.

# 2.3 APPROXILYZER: A FRAMEWORK FOR INSTRUCTION-LEVEL ERROR ANALYSIS

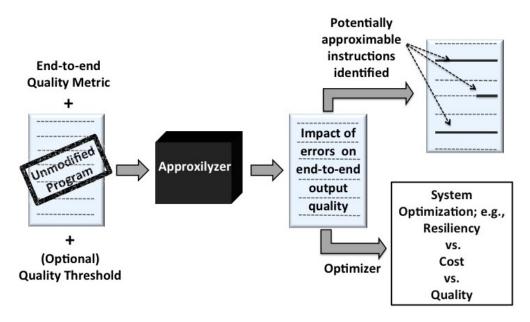

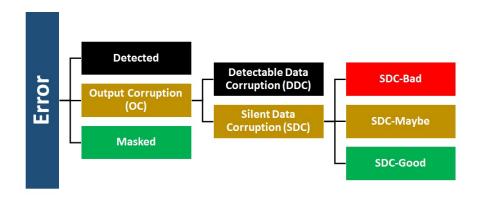

Approxilyzer builds upon Relyzer by introducing the notion of quality, determining the quality degradation for each predicted SDC, and applying this information in the areas of low cost resiliency and approximate computing. It takes as input an unmodified program (along with the application's input), a quality metric, and an optional acceptable quality threshold, and produces a comprehensive *output quality profile*. This profile provides the outcome of a single transient bit error in each error site in an execution. An outcome can be masked, detected, or an output corruption (OC), where output corruptions are further classified as either detectable data corruptions (DDCs) or silent data corruptions (SDCs). Additionally, SDCs are binned into buckets based on their output quality.

We demonstrate two uses of Approxilyzer. First, we show how Approxilyzer can be used to quantitatively tune output quality versus resiliency versus overhead to enable ultra-low cost resiliency solutions (with a single bit error model). For example, we show that Approxilyzer determines that a very small loss in output quality (1%) can yield large resiliency overhead reduction (up to 55%) for 99% resiliency coverage. Second, we show how Approxilyzer can be used to provide a first-order estimate of the approximation potential of general-purpose programs. It does so in an automated way while requiring minimal user input and no program modifications. This enables programmers or other tools to focus on the promising subset of approximable instructions for further analysis.

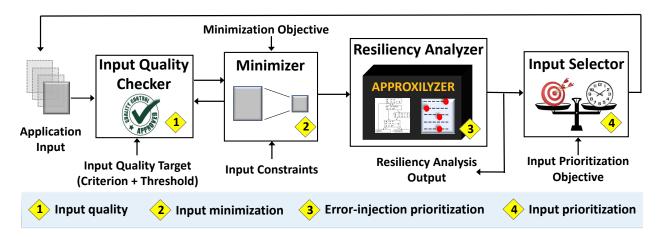

This section provides details of the Approxilyzer framework and its usage model, as illustrated in Figure 2.1.

#### 2.3.1 Inputs to Approxilyzer

Underlying any approximate computing solution is the need to quantify output quality through an end-to-end quality metric. This metric is domain-specific [74, 75, 76] and Approxilyzer assumes that the programmer or user will supply it. Approxilyzer uses this metric to calculate the quality degradation of the erroneous output with respect to an error-free output.

Another parameter pertinent to many use cases for approximation is the quality threshold that sets a bound on the maximum quality degradation that is acceptable to the user. This is an optional parameter that Approxilyzer can take as input from the user. Since programmers may want to use Approxilyzer for analysis or tuning, Approxilyzer enables them to specify quality threshold ranges if they so desire. In the limit, no threshold range may be specified,

Figure 2.1: Overview of the Approxilyzer framework and its usage.

in which case Approxilyzer will perform its analysis for the full range of quality degradation.

To assist the user, we incorporate simple domain-specific libraries in our framework that include common sense quality metrics and thresholds that a user can choose. For example, the maximum of the relative (percentage) difference between the golden and error-free output components, L2-norms of matrices, and absolute differences are examples of quality metrics that quantify the deviation of the erroneous output from the error-free one. Negative values and infinities are examples of obviously unacceptable outputs for many financial applications – the user can choose to apply acceptable thresholds based on such criteria. Section 2.4.1 describes specific metrics and thresholds used in our evaluation.

Thus, Approxilyzer places the absolute minimum burden on the user, only requiring an end-to-end quality metric and, optionally, acceptable quality thresholds.

#### 2.3.2 Classification of Errors

Approxilyzer aims to quantify the impact of a single bit transient error on the program's end-to-end output quality, for error sites comprising each register bit of each dynamic instruction in an execution. To accomplish this, Approxilyzer builds upon Relyzer [42], a tool to predict the outcomes of errors in all of the above error sites. Relyzer's predictions, however, only consider whether an error results in being masked (an output is produced and is the same as the golden, error-free output), detected (e.g., a fatal trap was invoked), or a silent data corruption (SDC). Relyzer does not consider output quality, marking all

Figure 2.2: A classification of errors.

corruptions in an output (no matter how trivial) as an SDC outcome.

Approxilyzer introduces a new categorization of error outcomes to incorporate the notion of output quality into the category of errors traditionally known as SDCs. Figure 2.2 depicts the new taxonomy of errors. We use the term **output corruption (OC)** to indicate the outcome of an error where the execution runs to completion without crashing the program, but where the output does not match up identically to that of the golden output. In the literature, such outcomes have previously been uniformly referred to as SDCs. However, we observe that there is a subclass of these previously classified SDCs that is, in fact, detectable and not strictly silent. Such outcomes can be detected using a variety of low-cost mechanisms such as range detectors [19, 21]. We introduce additional detectors in Approxilyzer to catch NaNs, infinity values, negative outputs (if not expected by an application), and a check to see if the final output of the erroneous execution generates the same number of values as the golden output, irrespective of deviation. Our categorization refers to the output corruptions detected through the above means as **detectable data corruptions (DDC)**. It refers to the remaining output corruptions, which are not detectable and truly silent, as silent data corruptions.

The SDCs are further categorized as follows:

- **SDC-Good:** These SDCs are *highly tolerable* output corruptions which produce negligibly small quality degradations. This category also includes outcomes where the deviations from the golden output occur only in non-significant portions of the output (e.g., program related statistics and timing information). These SDCs do not require any resiliency protection since errors produced by them are inherently tolerable. The threshold for "small errors" is application and metric dependant.

- *SDC-Maybe:* These are potentially tolerable SDCs. The entire class is not outright tolerable, but a subset of SDCs in this class may be tolerable based on user-provided ap-

plication quality constraints – usually in the form of an acceptable quality degradation threshold. Using Approxilyzer we show how we can extract SDCs that are tolerable from this class, tuning the output quality in accordance with cost- and reliability-benefits.

• **SDC-Bad:** These produce such large quality degradations that it can be reasonably assumed that they are not tolerable for most applications and users.

The above categorization of the SDCs is dependent on the domain-specific quality metric (required) and acceptable quality thresholds (optional) provided by the user. If a quality threshold is provided by the user, then whether an SDC is tolerable or not is a binary decision based on whether the resulting output quality degradation falls below or above the quality threshold. In the absence of user-provided quality thresholds (e.g., in cases where the user wants to undertake program analysis or tuning), Approxilyzer classifies the SDC error sites into SDC-Good, SDC-Bad, and SDC-Maybe. Note that the classification into SDC-Good and SDC-Bad occurs only if the user chooses to apply common sense domainspecific thresholds provided by the tool (Section 2.4.1). Otherwise, all the SDC error sites are classified as SDC-Maybe. For each error site belonging to the SDC-Maybe error class, Approxilyzer also records its associated output quality degradation. It assesses the quality of the corrupted/erroneous output by measuring its deviation from the error-free/precise output using the application-specific quality metrics provided by the user. For example, an error that produces a quality degradation of 20% is said to have a different outcome from one with a quality degradation of 25%. Hence, the output quality for a given error site is characterized by its error outcome class and additionally, in the case of SDC-Maybe, by the amount of quality degradation introduced in the output.

Approxilyzer hypothesizes that Relyzer's main insight (that errors propagating "similarly" through the program are likely to result in similar outcomes) also holds true when considering quality as part of the error outcome. That is, errors propagating "similarly" through the program are likely to generate program outputs of similar quality. Approxilyzer uses Relyzer's heuristics related to control and data flow to predict similarity and to divide error sites into equivalence classes (Section 2.2). We define validation experiments to test this hypothesis and show that this is indeed the case (Section 2.4). Thus, Approxilyzer is able to enumerate, with high confidence, the output quality generated when each single error site in the program is perturbed by a single bit corruption. We use the phrase "output quality of error site" to refer to the quality degradation in the output generated when an error is injected in the error site.

Table 2.1: Error outcomes and their potential for approximation and resiliency overhead savings.

| Error outcome category | Is this class of error sites approximable? | Does this class of error sites need resiliency protection? |

|------------------------|--------------------------------------------|------------------------------------------------------------|

| Masked                 | <b>✓</b>                                   | ×                                                          |

| SDC-Good               | /                                          | Х                                                          |

| SDC-Maybe              | Maybe                                      | Maybe                                                      |

| SDC-Bad                | Х                                          | ✓                                                          |

| DDC                    | Х                                          | ×                                                          |

| Detected               | Х                                          | Х                                                          |

# 2.3.3 Instruction-Level Approximation Opportunities

Given an unmodified program and end-to-end quality metrics, Approxilyzer analyzes the program and automatically provides the programmer with a set of instructions that are potential first order candidates for approximations. Approxilyzer does this by eliminating instructions that have unacceptable output quality. The underlying argument that Approxilyzer makes is that if an instruction produces an unacceptable quality output in the presence of single bit corruptions, then it is highly unlikely to generate an output of acceptable quality with more vigorous perturbations introduced by approximation.

Table 2.1 provides a classification of which error outcome categories are approximable and which are not. Error sites that produce Detected, DDC and SDC-Bad outcomes are clearly not acceptable and Approxilyzer marks them as not approximable. SDC-Good and Masked error sites are marked as approximable. SDC-Maybe error sites are potential candidates for approximation depending on whether their quality meets the acceptable quality threshold set by the user. The approximation potential of an instruction is decided based on the nature of its constituent error sites. If any error site in an instruction is deemed not approximable then the instruction is marked by Approxilyzer as not approximable. Otherwise, the instruction is marked as a potential candidate for approximation.

Since each error site in the application contains the information regarding which dynamic instance of an instruction it belongs to, Approxilyzer can identify dynamic instructions that can be approximated. This can be useful to determine if the application will benefit from approximation techniques at the dynamic instruction granularity (e.g., task skipping [77] and loop perforation [78]). Section 2.5.4 shows a case study for how Approxilyzer can be used to analyze applications for approximation potential.

Since our framework uses transient single bit errors as the error model, instructions marked as approximable by Approxilyzer may be false positives, since they may produce unacceptable quality output with approximation techniques that use different error models. False negatives, however, are expected to be rare since in most cases if a single bit upset in an

instruction causes an unacceptable outcome, then it is highly likely that multi-bit upsets will also result in unacceptable outcomes. While our approach is aggressive, we believe it is still useful since it narrows the huge exploration space for approximation to a manageable smaller set of instructions on which it is feasible to do further rigorous and targeted analysis. Another benefit of our approach is that the identification of approximable instructions is automatic and needs only minimal programmer input – end-to-end quality metrics and quality thresholds – and no program modifications. This makes it feasible even for novice programmers to analyze any program for hidden approximation opportunities.

## 2.3.4 Tuning Quality vs. Resiliency vs. Overhead

Approximate computing environments often trade accuracy in the program output for gains in other system parameters such as energy or performance. A framework like Approxilyzer, which quantifies the output quality of each error site in the program, can be used to tune the loss in output accuracy with respect to other system benefits. We study one such system benefit; namely, the reduction in the overhead costs related to resiliency. We describe how Approxilyzer can be used to tune overhead costs with respect to desired resiliency protection for different output quality requirements and show that this can enable ultra-low cost resiliency solutions (Section 2.5.3).

Approxilyzer uses its knowledge of each error site's output quality to decide whether that error site needs protection from transient errors (Table 2.1). Error sites that result in masked outcomes do not need to be protected since they produce the golden output even in the presence of transient errors. Low cost detectors (as discussed earlier) can be used to catch the detected category of errors and hence the associated error sites do not need to be protected.

In the absence of Approxilyzer, we would have to protect all OC error sites. With Approxilyzer's quality information, the system can selectively protect only those OCs that are neither tolerable by the user/application, nor can be protected by low cost detectors. Since SDC-Good is inherently tolerable and DDC (like detected) can be captured using other low cost detectors, these error sites need not be protected. SDC-Bad error sites produce intolerable outputs and hence they always have to be protected. SDC-Maybes may or may not need protection based on whether they meet the user's quality threshold. This reasoning about which error sites need protection from transient errors can be extended to instructions based on the quality of their constituent error sites. If an instruction contains an error site that needs to be protected, then we say that the instruction needs to be protected.

Thus, based on the type and quality of the OCs produced, Approxilyzer can selectively

tune the set of OC causing instructions chosen for protection from transient errors.

## 2.4 EVALUATION METHODOLOGY

### 2.4.1 Quality Assessment and Metrics

Table 2.2 details the applications, inputs, quality metrics, and quality threshold ranges used in our evaluations. To quantify the quality of the corrupted output, we must find a measure of its difference from the golden (error-free) output. We refer to this "difference measure" as the quality metric – technically, this is a quality degradation metric since the higher the value of the difference, the lower the quality.

Table 2.2: Applications, quality metrics, thresholds, and quality bins.

| Application        | Input                                | Metric                      | DDC                                                  | SDC-Good                                                          | SDC-Bad               | ${ m SDC	ext{-}Maybe} \ { m QB: \{Error\ range\}}$                                                                                                                                                                        |

|--------------------|--------------------------------------|-----------------------------|------------------------------------------------------|-------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blackscholes [79]  | sim-large                            | max-rel-err<br>max-abs-diff | $F_i > \$500$<br>$F_i < \$0$                         | $\begin{array}{c} \text{max-abs-diff} \\ < \$10^{-4} \end{array}$ | max-rel-err > 100%    | $\begin{array}{c} \text{max-rel-err:} \\ 1: \ \{10^{-4}\% \leftrightarrow 1\%\} \\ 2: \ \{1\% \leftrightarrow 2\%\} \\ \dots \\ 99: \ \{98\% \leftrightarrow 99\%\} \\ 100: \ \{99\% \leftrightarrow 100\%\} \end{array}$ |

| Swaptions [79]     | sim-small                            | max-abs-diff                | $F_i > \$500$<br>$F_i < \$0$                         | $\begin{array}{c} \text{max-abs-diff} \\ < \$10^{-4} \end{array}$ | max-abs-diff > \$1    | max-abs-diff:<br>1: $\{10^{-4} \leftrightarrow 10^{-3}\}$<br>2: $\{10^{-3} \leftrightarrow 10^{-2}\}$<br>3: $\{10^{-2} \leftrightarrow 10^{-1}\}$<br>4: $\{10^{-1} \leftrightarrow 1\}$                                   |

| LU [80]            | 512x512<br>matrix<br>16x16<br>blocks | max-rel-err                 | No<br>App-Specific<br>Detectors                      | ${\rm max\text{-}rel\text{-}err} < 10^{-4}\%$                     | max-rel-err<br>> 100% | max-rel-err:<br>same binning<br>as Blackscholes                                                                                                                                                                           |

| Water [80]         | 512<br>molecules                     | max-rel-err                 | No<br>App-Specific<br>Detectors                      | $\begin{array}{c} \text{max-rel-err} \\ < 10^{-4}\% \end{array}$  | max-rel-err > 100%    | max-rel-err:<br>same binning<br>as Blackscholes                                                                                                                                                                           |

| FFT [80]           | 64K<br>points                        | rel-l2-norm                 | No<br>App-Specific<br>Detectors                      | rel-l2-norm $< 10^{-4}\%$                                         | rel-l2-norm<br>> 100% | rel-l2-norm:<br>same binning<br>as Blackscholes                                                                                                                                                                           |

| Common to all apps |                                      |                             | $F_i = \text{NaN}$<br>$F_i = \text{Inf}$<br>#F != #G | Errors in non-<br>significant portions<br>of the output           |                       |                                                                                                                                                                                                                           |

In the absence of specific domain studies and standardization [74, 75, 76], we have done our best to choose quality metrics that strike a balance between over- and under-estimating an application's tolerance to errors. For example, consider outputs with multiple components. Without further guidance, we must first determine a difference function for each component and then a method to aggregate across the components. Depending on the magnitude of the individual components, we use the absolute difference (small magnitude) or the relative difference (large magnitude) for the per-component difference function. To aggregate across

components, we use the maximum instead of the average. In cases where there is an established common practice to analyze the output, we use the corresponding quality metric. For example, FFT produces a matrix and we use the relative difference in the bounded L2 norm to determine the quality.<sup>1</sup> More precisely, given a golden output G and a faulty output F, both having n components, where  $n \geq 1$ , Table 2.2 uses the following three quality metrics.

(1) max-abs-diff: This metric calculates the maximum absolute difference between the components of the golden and faulty outputs.

$$max-abs-diff = max(|G_1 - F_1|, |G_2 - F_2|, \dots, |G_n - F_n|)$$

(2.1)

(2) max-rel-err: This metric calculates the maximum of the relative error between the individual components of the golden and faulty outputs.

$$rel\_err_i = \frac{|G_i - F_i|}{G_i} \times 100 \tag{2.2}$$

$$max-rel-err = max(rel\_err_1, rel\_err_2, \dots, rel\_err_n)$$

(2.3)

(3) **rel-l2-norm**: This metric is typically used in mathematics to directly compare two matrices. The metric estimates the relative difference in the bounded L2 norms (BL2N) of the golden and erroneous matrices. For any matrix A, having n elements,  $a_1, a_2, \ldots, a_n$ , we define the following,

$$||A||_{BL2N} = \frac{||A||_{L2}}{n} \tag{2.4}$$

where,

$$||A||_{L2} = \sqrt{\sum_{i=1}^{n} a_i^2} \tag{2.5}$$

The rel-l2-norm is thus defined as:

$$rel-l2-norm = \frac{\|G - F\|_{BL2N}}{\|G\|_{BL2N}} \times 100$$

(2.6)

Table 2.2 also lists the quality threshold ranges for identifying SDC-Good and SDC-Bad. We use fairly conservative values that we believe will be reasonable for most users and applications.

Finally, although output quality is a continuous function, for ease of analysis and comparison, we discretize it into multiple  $Quality\ Bins\ (QB)$ , fine-grained enough to capture small

<sup>&</sup>lt;sup>1</sup>We do not use this for LU because it effectively produces two triangular matrices and how the errors in the two are composed depends on how the output is used.

quality variations (last column of Table 2.2). For example, with the *max-rel-err* metric, the bins are 1% wide (except at the boundary), and quality values of 12.1%, 12.6% and 13.3% are assigned a QB of 13, 13, and 14 respectively. Thus, SDC-Maybe with QB10 refers to an SDC-Maybe outcome with an output quality degradation in the range specified by QB10.

### 2.4.2 Error Injection Framework

Our error injection simulation infrastructure for Approxilyzer is similar to that used for Relyzer [42]: it is based on Wind River Simics [71] and GEMS [81] for running our applications on OpenSolaris and compiled to the SPARC V9 ISA.

We inject single bit flips in integer and floating point architectural registers. Hence, we only consider instructions that employ either an integer or floating point register as an operand. For example, we do not inject errors in instructions such as *call* (no operands), *ret* (no operands) or branches that use special condition code registers. Such instructions will not be considered for approximation or resiliency protection.

We perform error injections only in the pilots of the generated equivalence classes. This can still lead to a large number of error injections, especially for longer applications. In order to reduce the simulation time, we only study 99% of the error sites in the application for Approxilyzer, thereby trading off simulation time for a modest loss in coverage [42]. The 1% of error sites not included in the study do not detract from the observations and gains reported.<sup>2</sup> For resiliency overhead tuning (Section 2.5.3), these unexplored error sites might represent missed opportunity (in the event that they produce SDCs) for further overhead reduction using Approxilyzer. When identifying approximable instruction (Section 2.5.4), these remaining error sites might introduce some false positives (in the event that they produce unacceptable errors). This is, however, consistent with our goal to tolerate some false positives, while minimizing false negatives, in the quest to uncover approximation opportunities in the application.

Approxilyzer retains Relyzer's speed benefits, with negligible additional overheads. Compared to a (hypothetical) framework that would perform an error injection for each error site, Relyzer is able to prune error injections by 3 to 5 orders of magnitude [42]. The remaining error injections complete on our cluster of 200 machines in a few days. Approxilyzer adds a few hours to this process to perform quality calculations and error outcome categorizations. The analysis to generate quality versus resiliency versus overhead curves for an application (Section 2.5.3) takes several minutes. Analyzing error outcomes and quality to

$<sup>^2</sup>$ We address the remaining 1% of error sites in Chapter 3 by performing *input minimization* to reduce the total number of error sites, making 100% error site evaluation feasible.

identify approximable instructions (Section 2.5.4) takes a few seconds per application.

## 2.4.3 Validation Methodology

Approxilyzer relies on Relyzer's heuristics to group error sites that produce similar quality outcomes into an equivalence class (Section 2.3.2). It predicts the quality of each element of an equivalence class based on the outcome of a fault injection experiment on its pilot. To validate these predictions, we perform experiments similar to those in Relyzer [42].

The validation experiment asks the question: how accurately does the output quality of the pilot predict the output quality of the other error sites in its equivalence class? For validating a single pilot, we perform error injections in a sample of error sites from the pilot's equivalence class. We then compare the output quality of the population with that of the pilot to gain confidence that the pilot accurately represents the population, and hence the equivalence class. For example, a pilot that produces a DDC has a 100% validation/prediction accuracy if the injection experiments for all of its associated population also produced DDCs. If only 90% of the population produced a DDC, the pilot's prediction accuracy is 90%.

To validate a pilot of an SDC-Maybe class, we further require that the QB of the pilot match that of the population to be considered a correct prediction. For example, consider a pilot X that generates an SDC-Maybe with QB12. Suppose 86% of its population is SDC-Maybe with QB12, 6% is SDC-Maybe with QB13, 5% is SDC-Maybe with QB10, and 3% is SDC-Bad. Then the prediction accuracy of pilot X is 86%.

The overall prediction accuracy for an application is obtained by calculating the average of the prediction accuracy across all the pilots studied, weighted by the size of their equivalence class.

Requiring the pilot's QB to exactly match the QB of the associated population is unnecessarily conservative and a tall order for any tool, especially for outcomes with quality at the QB boundaries. We therefore introduce a flexibility parameter,  $\delta$ , that allows a fine-grained margin of error at QB boundaries. For the validation of pilot X described above, setting  $\delta = x$  means that an error site in its population with QB of  $12 \pm x$  would be considered as a correct prediction. Thus, pilot X's prediction accuracy with  $\delta = 1$  is 92% and with  $\delta = 2$  is 97%. The baseline validation uses the setting  $\delta = 0$ .

We can further loosen our constraints on validation by considering the context in which Approxilyzer is used as follows:

• Validation for Resiliency: In the first case, Approxilyzer is used to determine which instructions need to be protected for resiliency. We therefore do not need to distinguish

between Masked, SDC-Good, DDC, and Detected outcomes since all of them do not require protection. We therefore group these outcomes together.

• Validation for Approximation: In the second case, Approxilyzer is used to determine which instructions are approximable. We therefore do not need to distinguish between Masked and SDC-Good outcomes since they are approximable, and can group them together. Similarly, we can group SDC-Bad, DDC, and Detected outcomes together since they are not approximable.

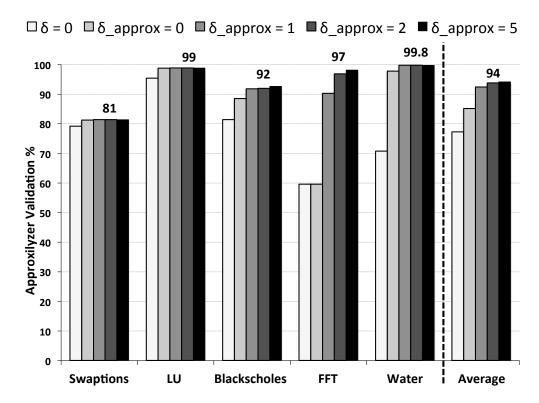

Thus, for a given use case, a pilot is said to have a correct prediction for a member of its equivalence class if both the pilot and the member produce an outcome within the same group as defined above for the use case. We use  $\delta_{res}$  and  $\delta_{approx}$  when considering use-specific validations for resiliency and approximation respectively. We continue to use  $\delta$  for use-oblivious validations.

As an example, consider a Pilot Y that generates a DDC and has the following population outcome distribution: DDC: 85%, Detected: 7%, SDC-Good: 5% and SDC-Bad: 3%. The prediction accuracy of Y is 85% for  $\delta = 0$ , 97% for  $\delta_{res} = 0$ , and 95% for  $\delta_{approx} = 0$ .

We perform the validation experiments for  $\sim 700$  pilots from each application. This gives us a 99% confidence interval with a 5% error margin. We validate each pilot against a sample population size of 750 (drawn randomly from the equivalence class), which also gives us a statistical confidence of 99% with a 5% error margin. In all, we perform approximately 2.6 million error injection experiments for validating Approxilyzer.

#### 2.5 RESULTS

We begin the evaluation in Section 2.5.1 by showing the output corruption distribution as analyzed by Approxilyzer, followed by validation results in Section 2.5.2. Section 2.5.3 describes Approxilyzer results for tuning an application's quality versus resiliency versus overhead tradeoffs. Section 2.5.4 shows how Approxilyzer can be used to identify approximable instructions in an application, using the duality of the tool for resilience and approximation purposes.

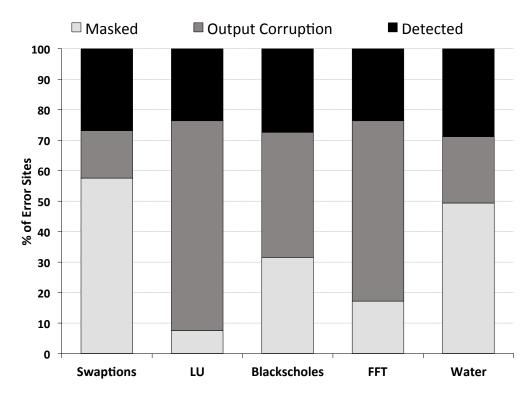

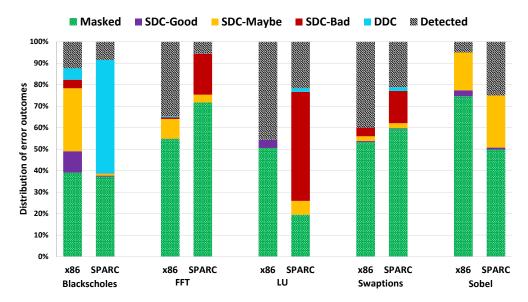

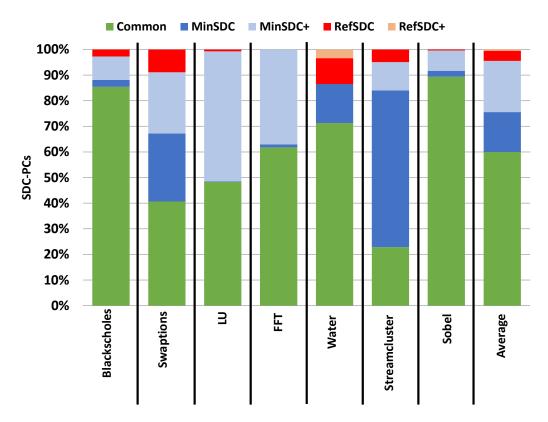

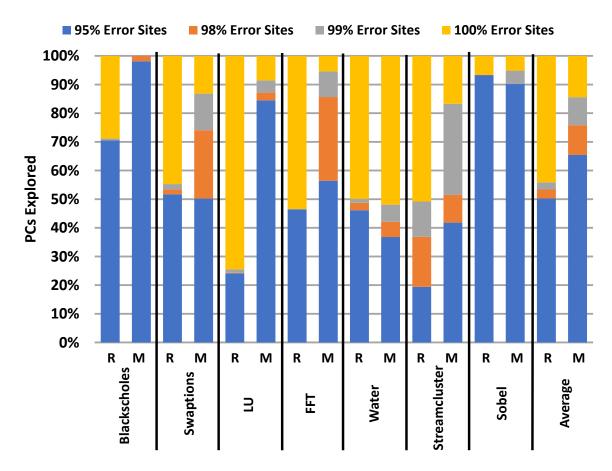

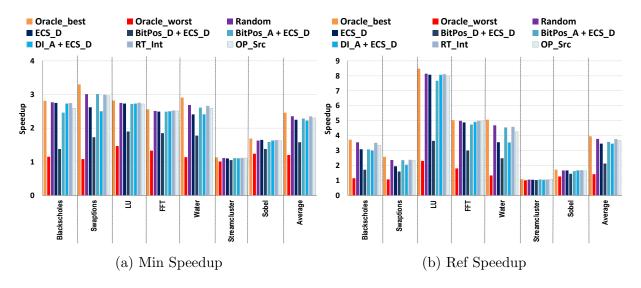

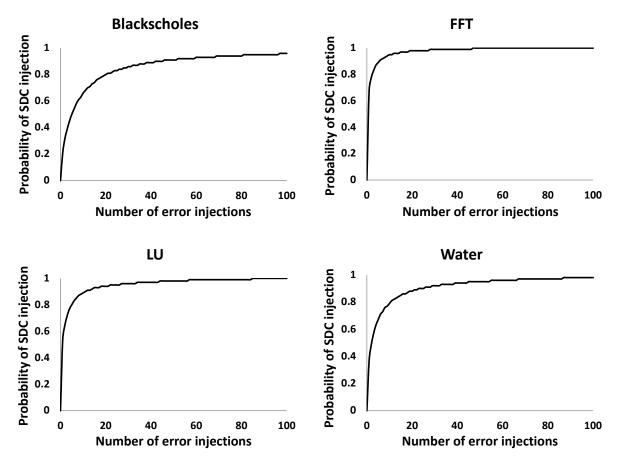

Figure 2.3: Distribution of error outcomes for the applications studied.

#### 2.5.1 Output Corruption Distribution

Figure 2.3 shows the distribution of outcomes for error sites in the studied applications.<sup>3</sup> Each application exhibits a unique distribution of error outcomes. At 68.8%, LU contains the highest percentage of Output Corruption (OC) causing error sites and Swaptions, at 15.6%, the lowest.

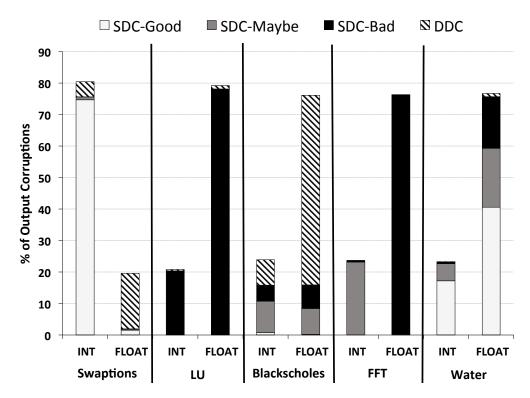

Figure 2.4 shows the different categories of output corruptions, separately for integer and floating point register error sites. Swaptions and Water show very high percentage of SDC-Good at 76% and 58% respectively while Blackscholes produces 68% DDC (for both Integer and Float combined). Swaptions and FFT show an interesting dichotomy in the behavior of errors in the integer versus floating point registers, implying perhaps, a need for separate techniques for resiliency and approximation across the two different register classes. LU's OC error sites are almost exclusively (>98%) composed of SDC-Bad outcomes. This may either imply that LU is inherently not tolerant to errors or that the quality metric used to classify errors in the output of LU may not be the correct choice.

These results illustrate how Approxilyzer can be employed to automatically analyze an

<sup>&</sup>lt;sup>3</sup>The OC (originally SDC) rates reported in this work are different from the rates reported in previous work [21, 42] as our error model is different. We study errors in both integer and floating point architectural registers, while our prior work only considered integer registers.

Figure 2.4: Distribution of output corruptions (OC) in integer (INT) and floating point (FLOAT) registers.

application to gain insights into its behavior in the presence of perturbations.

#### 2.5.2 Validation

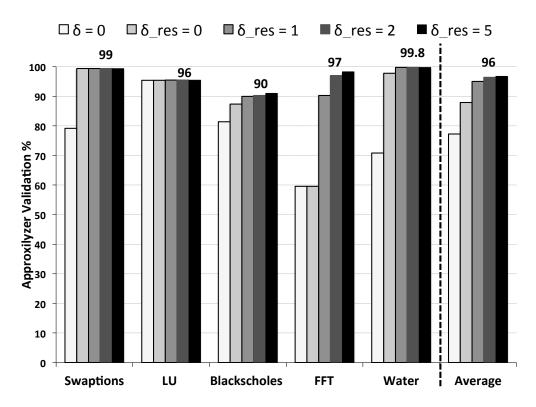

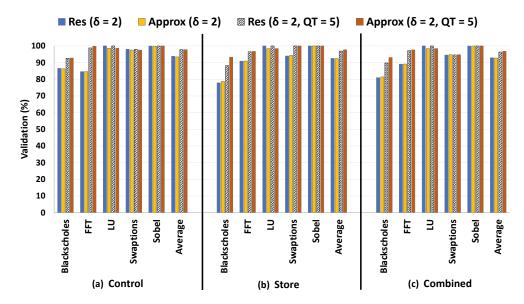

Validation results for resiliency: The results for validation geared towards resiliency are shown in Figure 2.5. All of the applications show very high pilot prediction rates with an average prediction rate of 96% across applications using a very fine quality window of 2 (i.e.,  $\delta_{res} = 2$ ).

Swaptions and Water see big gains in validation just by applying the  $\delta_{res}$  optimization. Both of these applications have high SDC-Good rates (Figure 2.4) and therefore many pilots that are picked for validation belong to the SDC-Good outcome category. Some of these equivalence classes (with SDC-Good pilots) contain a mix of Masked and SDC-Good error sites, leading to lower overall validation for  $\delta = 0$ .

Water especially has a high rate of SDC-Good outcomes which are due to very small errors ( $< 10^{-6}\%$ ) in the program statistics part of the output file. Approxilyzer heuristics (not surprisingly) combine these error sites with Masked outcomes into equivalence classes. As a result, applying the  $\delta_{res}$  optimization causes the validation rate of Water to jump from

Figure 2.5: Approxilyzer validation geared towards resiliency.

71% to 98%.

In addition to having equivalence classes with mixed SDC-Good and Masked outcomes (as described above for Water), Swaptions also has some pilots with DDC outcomes (Figure 2.4) belonging to equivalence classes that feature a mix of DDC and Masked outcomes. These pilots represent error sites from a few floating point instructions that process randomly generated numbers. If the error causes the random number to exceed the (expected) range of 0 to 1, it causes floating point overflows which result in NaN values. Because Approxilyzer heuristics cannot accurately distinguish this special case, Swaptions contains some equivalence classes with a mix of Masked and DDC outcomes which results in poor validation for  $\delta = 0$ . Applying the  $\delta_{res}$  optimization, causes the validation rate of Swaptions to go up from 79% to 99%.

While still high at 90% (for  $\delta_{res} = 2$ ), Blackscholes shows the lowest validation accuracy of the applications studied. Further analysis shows that this is due to a few pilots whose equivalence classes have a mix of SDC-Maybe and SDC-Bad outcomes. This is why increasing the quality window size ( $\delta$ ) does not cause the prediction rate to increase. The reason behind the mixed equivalence class can be attributed to the fact that Blackscholes calculates the option price for a portfolio containing more than 64,000 options and hence, the same

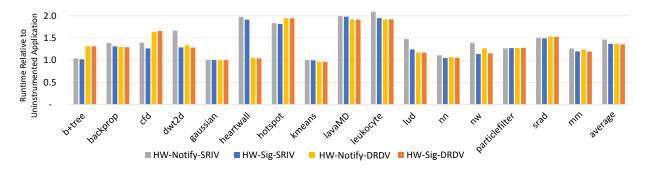

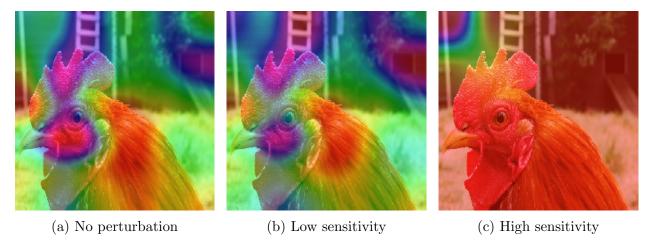

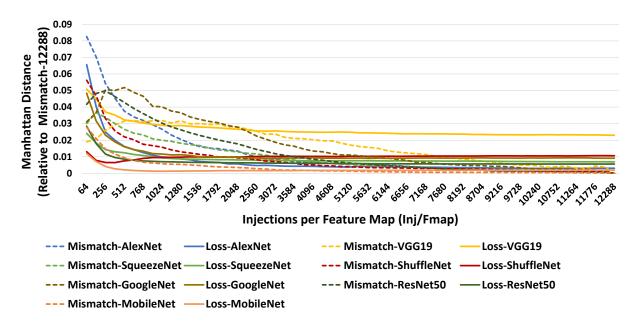

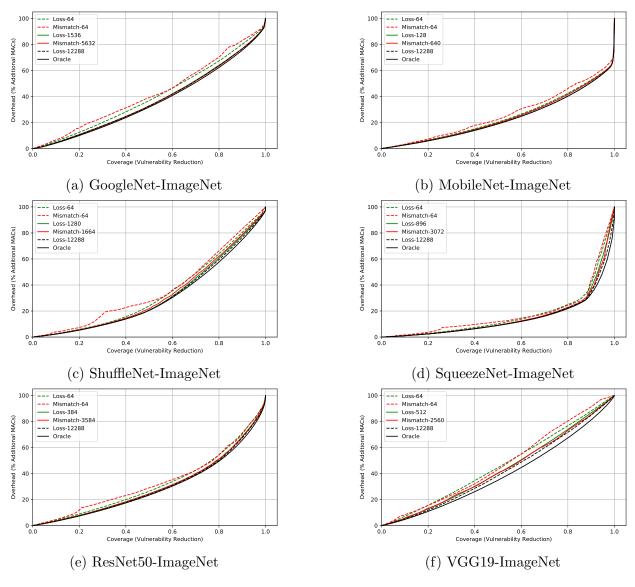

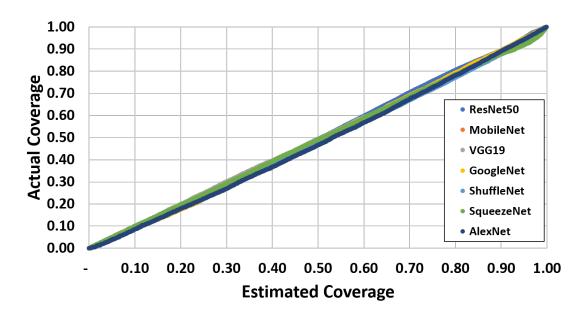

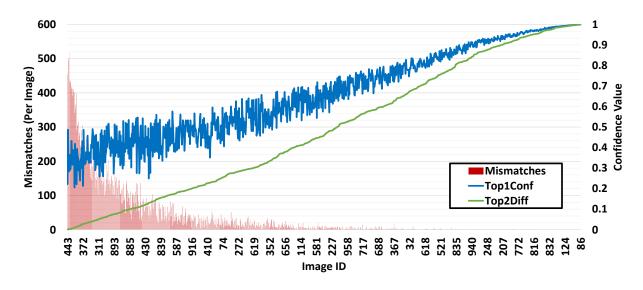

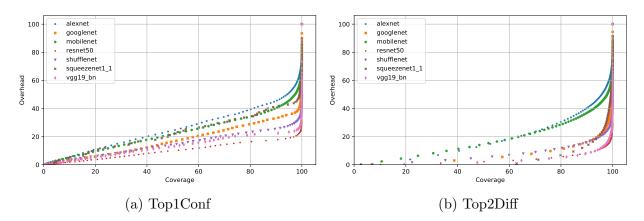

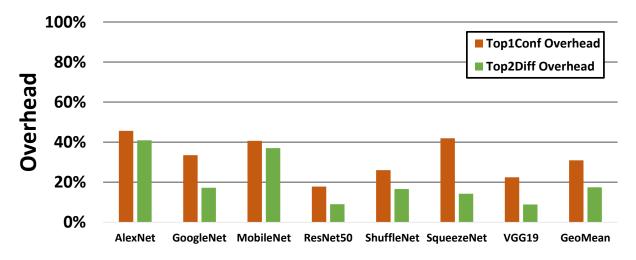

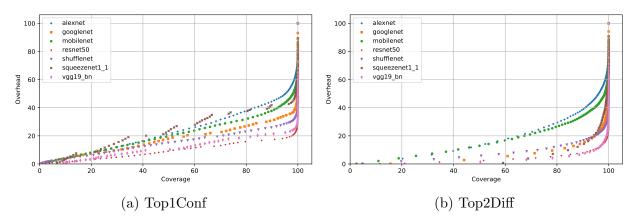

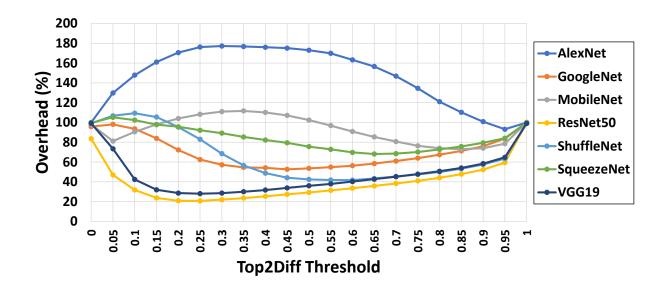

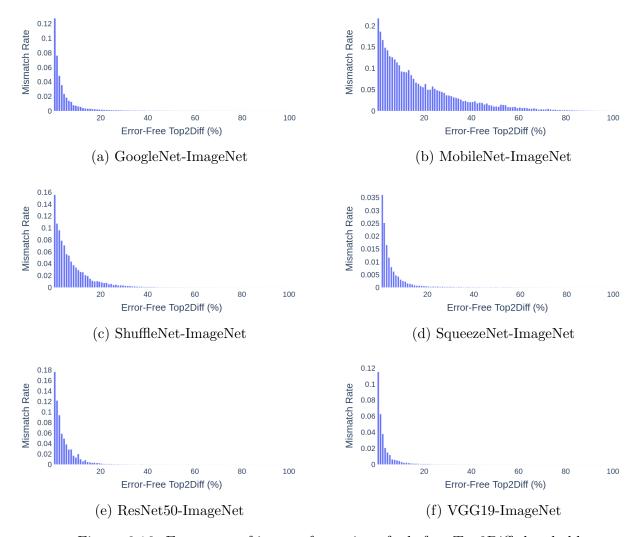

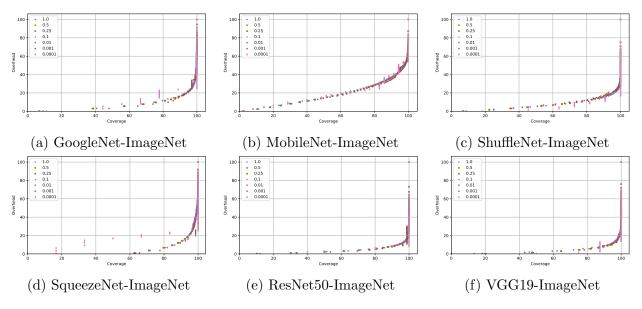

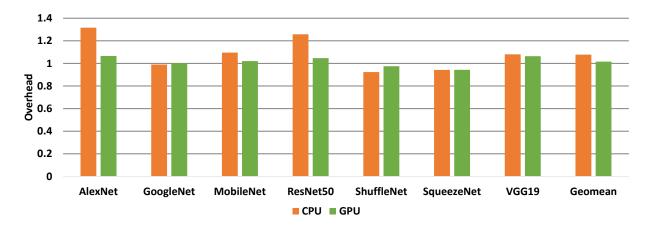

Figure 2.6: Approxilyzer validation geared towards approximation.