Center for Reliable and High-Performance Computing

## A Framework for Exploiting Data and Functional Parallelism on Distributed Memory Multicomputers

Shankar Ramaswamy, Sachin Sapatukar and Prithviraj Banerjee

Coordinated Science Laboratory College of Engineering UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

| UNCLASSIFIED<br>SECURITY CLASSIFICATION OF THIS PAGE                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                   | REPORT DOCU                                                                                                                                                                                                                                                                                                              | MENTATION                                                                                                                                                                                  | PAGE                                                                                                                                                                                            |                                                                                                                               |                                                                                      |

| 1a. REPORT SECURITY CLASSIFICATION                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          | 1b. RESTRICTIVE                                                                                                                                                                            | MARKINGS                                                                                                                                                                                        |                                                                                                                               |                                                                                      |

| Unclassified                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                          | None<br>3. DISTRIBUTION/AVAILABILITY OF REPORT                                                                                                                                             |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| 2a. SECURITY CLASSIFICATION AUTHORIT                                                                                                                                                                                              | Y .                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                            | for public r                                                                                                                                                                                    |                                                                                                                               |                                                                                      |

| 2b. DECLASSIFICATION / DOWNGRADING SCHEDULE                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            | ion unlimite                                                                                                                                                                                    |                                                                                                                               |                                                                                      |

| 4. PERFORMING ORGANIZATION REPORT                                                                                                                                                                                                 | NUMBER(S)                                                                                                                                                                                                                                                                                                                | 5. MONITORING                                                                                                                                                                              | ORGANIZATION RE                                                                                                                                                                                 | PORT NUMB                                                                                                                     | ER(S)                                                                                |

|                                                                                                                                                                                                                                   | CRHC 94-10                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                            |                                                                                                                                                                                                 | ·                                                                                                                             |                                                                                      |

| 6a. NAME OF PERFORMING ORGANIZATI                                                                                                                                                                                                 | ON 6b. OFFICE SYMBOL                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                            | ONITORING ORGAN                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| Coordinated Science Lab                                                                                                                                                                                                           | (If applicable)                                                                                                                                                                                                                                                                                                          | Office of Naval Research                                                                                                                                                                   |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| University of Illinois                                                                                                                                                                                                            | N/A                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                               | Administration                                                                       |

| 6c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                          | 7b. ADDRESS (CA                                                                                                                                                                            | ty, State, and ZIP Connection, VA 22                                                                                                                                                            | 2217                                                                                                                          |                                                                                      |

| '1308 W. Main St.                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            | fett Field, (                                                                                                                                                                                   |                                                                                                                               |                                                                                      |

| Urbana, IL 61801                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 | Rear Ser                                                                                                                      |                                                                                      |

| 8a. NAME OF FUNDING / SPONSORING                                                                                                                                                                                                  | 8b. OFFICE SYMBOL                                                                                                                                                                                                                                                                                                        | 9. PROCUREMEN                                                                                                                                                                              | T INSTRUMENT IDE                                                                                                                                                                                | NTIFICATION                                                                                                                   | NUMBER                                                                               |

| ORGANIZATION<br>7a                                                                                                                                                                                                                | (If applicable)                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          | 10 SOURCE OF                                                                                                                                                                               | FUNDING NUMBERS                                                                                                                                                                                 | 5                                                                                                                             |                                                                                      |

| 8c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                          | PROGRAM                                                                                                                                                                                    | PROJECT                                                                                                                                                                                         | TASK                                                                                                                          | WORK UNIT                                                                            |

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          | ELEMENT NO.                                                                                                                                                                                | NO.                                                                                                                                                                                             | NO.                                                                                                                           | ACCESSION NO.                                                                        |

| 7b<br>11. TITLE (Include Security Classification)                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            | and the second second                                                                                                                                                                           |                                                                                                                               |                                                                                      |

|                                                                                                                                                                                                                                   | MY, Shankar, Sachin S                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                            | nd Prithviraj<br>ORT (Year, Month, D                                                                                                                                                            | Banerjee                                                                                                                      | alticomputers                                                                        |

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          | 94-06-2                                                                                                                                                                                    | 21                                                                                                                                                                                              |                                                                                                                               | 38                                                                                   |

| 16. SUPPLEMENTARY NOTATION                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                         |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| 17. COSATI CODES                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                          | MS (Continue on reverse if necessary and identify by block number)                                                                                                                         |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| FIELD GROUP SUB-GR                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                               | ow graphs, graph                                                                     |

|                                                                                                                                                                                                                                   | ical programm                                                                                                                                                                                                                                                                                                            | ing, processo                                                                                                                                                                              | or allocation                                                                                                                                                                                   | , schedul                                                                                                                     | Ling, DMM                                                                            |

| 19. ABSTRACT (Continue on reverse if i                                                                                                                                                                                            | necessary and identify by block                                                                                                                                                                                                                                                                                          | number)                                                                                                                                                                                    | 12. C. 1                                                                                                                                                                                        |                                                                                                                               |                                                                                      |

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                               |                                                                                      |

| either pure data paralleli<br>framework for deciding on<br>and data parallelism in th<br>and communication cost f<br>costs and show that these<br>functional and data para<br>programming tool. Curren<br>Machines CM-5 and Intel | ave shown the benefits of i<br>sm or pure functional paral<br>in a good execution strategy<br>e program. The framework is<br>functions for multicomputer<br>e functions are realistic. The<br>allelism for a given problem<br>ntly, we have tested our appr<br>Paragon. Results presented<br>ase in speedups over approa | lelism. The work<br>for a given progr<br>s based on assumy<br>systems. We press<br>e framework also<br>n. For this purp<br>roach using three is<br>show that the app<br>ches using only da | in this paper pro-<br>am based on the<br>ptions about the for-<br>sent mathematical<br>requires specificat<br>oose, we have dev<br>benchmark progra<br>roach is very effect<br>ata parallelism. | esents a the<br>available fu<br>form of comp<br>l functions f<br>zion of the a<br>veloped a g<br>ums on the T<br>tive and can | eoretical<br>nctional<br>putation<br>for these<br>available<br>graphical<br>Fhinking |

| 20. DISTRIBUTION / AVAILABILITY OF A                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            | SECURITY CLASSIFIC                                                                                                                                                                              | CATION                                                                                                                        |                                                                                      |

| UNCLASSIFIED/UNLIMITED                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                          | RS Unclass<br>22b. TELEPHON                                                                                                                                                                | E (Include Area Code                                                                                                                                                                            | e) 22c. OFFI                                                                                                                  | CE SYMBOL                                                                            |

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                                 | 1                                                                                                                             |                                                                                      |

| DD FORM 1473, 84 MAR                                                                                                                                                                                                              | 83 APR edition may be use<br>All other editions a                                                                                                                                                                                                                                                                        | d until exhausted.<br>re obsolete.                                                                                                                                                         |                                                                                                                                                                                                 |                                                                                                                               | TION OF THIS PAGE                                                                    |

|                                                                                                                                                                                                                                   | All other editions a                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                            | UNCLAS                                                                                                                                                                                          | SSIFIED                                                                                                                       |                                                                                      |

## A Framework for Exploiting Data and Functional Parallelism on Distributed Memory Multicomputers \*

Shankar Ramaswamy<sup>†</sup>, Sachin Sapatnekar<sup>‡</sup> and Prithviraj Banerjee<sup>†</sup>

† Center for Reliable and High Performance Computing Coordinated Science Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 ‡ Dept of EE/CprE222 Coover HallIowa State UniversityAmes, IA 50011

## Tel : (217)333-6564 Fax : (217)244-5685 E-mail : shankar,banerjee@crhc.uiuc.edu

#### Abstract

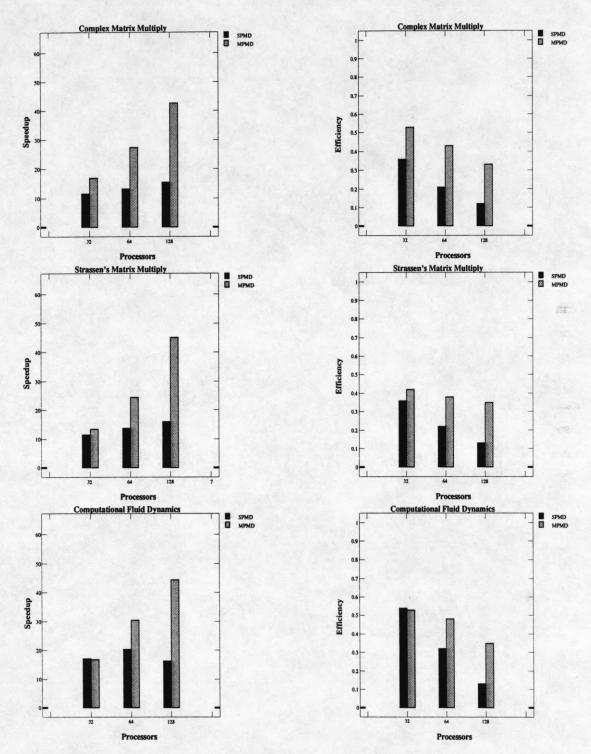

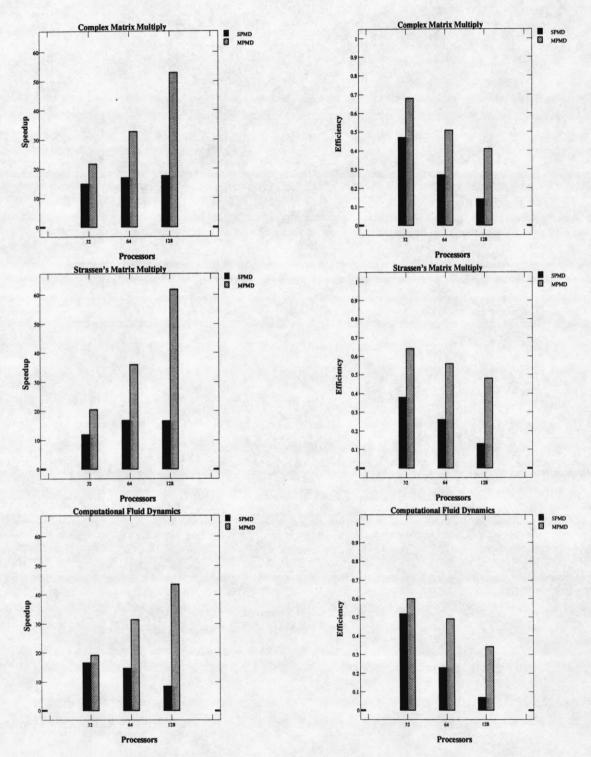

Recent research efforts have shown the benefits of integrating functional and data parallelism over using either pure data parallelism or pure functional parallelism. The work in this paper presents a theoretical framework for deciding on a good execution strategy for a given program based on the available functional and data parallelism in the program. The framework is based on assumptions about the form of computation and communication cost functions for multicomputer systems. We present mathematical functions for these costs and show that these functions are realistic. The framework also requires specification of the available functional and data parallelism for a given problem. For this purpose, we have developed a graphical programming tool. Currently, we have tested our approach using three benchmark programs on the Thinking Machines CM-5 and Intel Paragon. Results presented show that the approach is very effective and can provide a two- to three-fold increase in speedups over approaches using only data parallelism.

<sup>\*</sup>This research was supported in part by the Office of Naval Research under Contract N00014-91J-1096, and in part by the National Aeronautics and Space Administration under Contract NASA NAG 1-613.

## 1 Introduction

Distributed Memory Multicomputers such as the IBM SP-1, the Intel Paragon and the Thinking Machines CM-5 offer significant advantages over shared memory multiprocessors in terms of cost and scalability. Unfortunately, to extract all that computational power from these machines, users have to write efficient software for them, which is an extremely laborious process. Numerous research efforts have proposed language extensions to FORTRAN in order to ease programming multicomputers; the most prominent one has been the HPF language standardization [1]. A number of compilers for HPF have been proposed; these include the FORTRAN-D compiler from Rice University [2], the SUIF compiler from Stanford [3], the PTRAN II compiler from IBM [4], the SUPERB compiler from the University of Vienna [5], and, the FORTRAN-90D/HPF compiler from Syracuse University [6].

The PARADIGM compiler project at Illinois is aimed at devising a parallelizing compiler for distributed memory multicomputers that will accept FORTRAN 77 or HPF programs as input. The fully implemented PARADIGM compiler will:

- Annotate FORTRAN 77 programs with HPF data distribution directives [7, 8].

- Partition computations and generate communication for HPF programs [9, 10, 11].

- Exploit functional and data parallelism in HPF programs [12, 13, 14, 15].

- Provide runtime support for irregular computations [16].

There has been a lot of interest in simultaneous exploitation of data and functional parallelism. Research efforts in the area include the Fx compiler from CMU [17], the FORTRAN-M compiler from Argonne National Lab [18], the work by Chapman et. al. in [19], the work by Cheung and Reeves in [20], the work by Girkar and Polychronopoulos in [21], and, the work by Ramaswamy and Banerjee in [22]. All these efforts recognize the benefits of using both types of parallelism together to achieve better performance for certain applications. In this paper, we have discussed the framework to be used in the PARADIGM compiler for exploiting functional and data parallelism together.

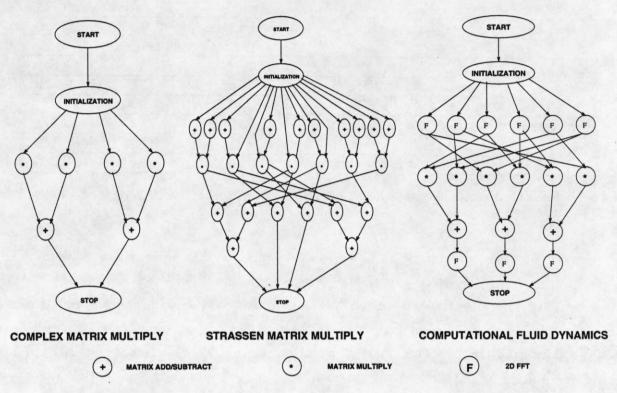

For our discussion, we define *Functional Parallelism* to be any parallelism existent among the various routines of a given program and *Data parallelism* to be parallelism within a routine that is obtained by distributing data among all processors involved and having them each perform computation using the owner computes rule [2]. Matrix Add, Matrix Multiply and 2D FFT are a few examples of what we mean by routines. To re-emphasize, the definitions of functional and data parallelism above may not correspond to some of the other popular connotations of these terms.

#### 1.1 Macro Dataflow Graphs

In order to expose the parallelism available in any given program, we use a representation called the *Macro Dataflow Graph* (MDG). This representation has been used before by researchers such as Sarkar in [23] and Prasanna and Agarwal in [24]. For our work, the MDG representation for a program is defined to be a weighted directed acyclic graph whose nodes correspond to routines of the program and edges correspond to precedence constraints among these routines. There are two distinguished nodes in the MDG called START and STOP. START precedes all other nodes and STOP succeeds all other nodes.

The weights of the nodes and edges are based on the concepts of *Processing* and *Data Transfer* costs. The time required for the execution of a routine is called its processing cost. Processing costs will depend on the number of processors used to execute the routine and include all computation and communication costs incurred. On distributed memory machines these costs will be dependent on the kind of data distribution used. Each routine may need a particular distribution for each of its arrays to achieve the best performance. Since precedence constraints mean that an array being read by a routine is being written into by its predecessor, we may need to redistribute the array after the execution of the predecessor routine. The time needed for this data redistribution between the execution of a pair of routines is referred to as the data transfer cost for that pair. Data transfer costs are made up of three components : a sending cost for processors at the sending routine, a network cost, and, a receiving cost for processors used for the sending and receiving routines.

We consider the weight of a node in the MDG to be composed of:

- 1. The receiving cost components of all data transfers from its predecessors

- 2. The processing cost of the routine it corresponds to

- 3. The sending cost components of all data transfers to its successors

The two distinguished nodes START and STOP do not perform any computation, they have zero weight.

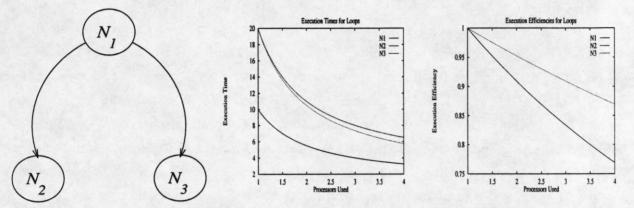

Figure 1: Example Showing Functional Parallelism

The weight of an edge between a pair of nodes in the MDG is taken to be the network cost component of data transfer between the routines corresponding to the nodes.

The usefulness of MDGs is that they can be used to decide on the strategy to be used to minimize execution time of the given program on the target multicomputer. MDGs expose functional and data parallelism in the program, allowing us to exploit both in an optimal manner. Data parallelism information is implicit in the weight functions of the nodes and functional parallelism is implicit in the precedence constraints among nodes. In order to decide on a good execution strategy for a program, we use an *Allocation and Scheduling* approach. Allocation decides on the number of processors to use for each node in the MDG and scheduling decides on a scheme of execution for the allocated nodes on the target multicomputer. Our work in this paper provides methods that allocate and schedule any given MDG such that the finish time obtained is within a factor of the best finish time theoretically obtainable.

#### 1.2 Example

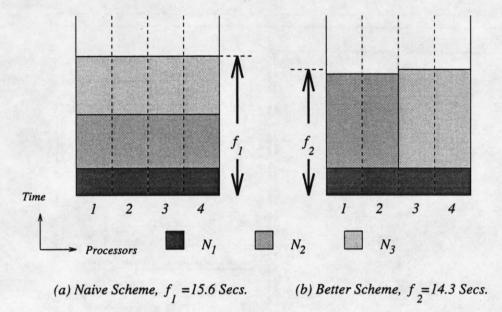

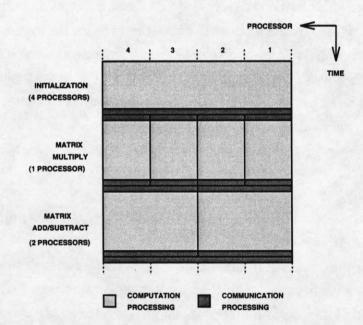

The usefulness of good allocation and scheduling may not be clear at first sight. It can be better appreciated by considering an example. Figure 1 shows an MDG with three nodes  $N_1$ ,  $N_2$  and  $N_3$ . Plotted alongside are the processing costs of the routines they correspond to as a function of the number of processors used. For ease of understanding we assume there are no data transfer costs between routines. By our definitions, the weights of the nodes in this MDG would be the same as the corresponding processing costs and the weight of edges would be 0. Now, given a system with 4 processors, there could be many ways in which we can allocate and schedule the MDG. For instance, a naive scheme would be to execute the nodes one after another on all 4 processors. In this case, we have an execution time of 15.6 seconds. On the other hand, a better way of executing the MDG would be to first execute  $N_1$  on all 4 processors, then allocate 2 processors each to nodes  $N_2$  and  $N_3$  and execute them concurrently. This way, the routines finish in 14.3 seconds. The two schemes are shown pictorially in Figure 2. The first scheme is exploiting pure data parallelism, i.e., all routines use 4 processors. The second scheme on the other hand, is exploiting both functional and data parallelism, i.e., routines 2 and 3 execute concurrently as well as use 2 processors each.

Intuitively, good allocation and scheduling makes program execution faster because of more efficient execution. Most real applications execute more inefficiently as the size of a processor system grows, the processing efficiency curves of Figure 1 in our example are typical. We can see that by executing the nodes  $N_2$  and  $N_3$  concurrently and using fewer processors for them, the second scheme improves overall efficiency over the first. This makes the second scheme execute the program faster than the first.

A point of interest with respect to the type of code generated in the two schemes is that the first scheme will essentially have each processor execute similar code on different data sets. We refer to this type of code as Single Program Multiple Data (SPMD). On the other hand, the second scheme can have very different code for each processor; this type of code is called Multiple Program Multiple Data (MPMD). Therefore, SPMD code exploits only data parallelism while MPMD code exploits both data and functional parallelism.

## 1.3 Allocation and Scheduling

The basic problem of optimally scheduling a set of nodes with precedence constraints on a p processor system when each node uses just one processor has been shown to be NP-complete by Lenstra and Kan in [25]. Further treatment on this topic can also be found in the book by Garey and Johnson [26]. The allocation and scheduling problem is considerably harder than the one just described. There have been two major approaches to the approximate solution of the allocation and scheduling problem. The first has been a bottom up approach like those used by Sarkar in [23], and Gerasoulis and Yang in [27, 28]. A bottom up approach considers the MDG to be made up of lightweight nodes (in terms of computation requirements) with each using only one processor (an explicit allocation is not done). The bottom up scheduling methods of [23, 27, 28] then use clustering on the nodes to form larger nodes during the construction of a schedule. The second approach to allocation and scheduling is a top down approach like the ones used by Prasanna and Agarwal in [24],

Figure 2: Allocation and Scheduling Schemes for Example

Belkhale and Banerjee in [12, 13], by Subhlok et. al. in [17, 29, 30], by Ramaswamy and Banerjee in [14, 15] and in this paper. Top down approaches start with the assumption of heavyweight nodes (again, in terms of computation requirements) in the MDG and break them down during the process of constructing an optimal schedule. Top down methods are considered better in that they take a more global view of the problem than the bottom up approaches. Therefore they may be able to perform better optimizations.

The difference between earlier top down approaches mentioned above and the work presented here is significant. The methods presented in [24] do not consider data transfer costs between nodes of the MDG. In addition, they make simplifying assumptions about the type of MDGs handled and the processing cost model used. We do not make any assumptions for our MDGs and use very realistic cost models. The work in [12, 13] also does not consider the effects of non-zero data transfer costs. Their allocation and scheduling algorithms are similar to the ones we use. The research presented in [17, 29, 30] considers allocation and scheduling for a class of problems that process continuous streams of data sets. The computation for each data set has a tree-structured MDG for all their benchmark programs [31]. A set of heuristics are used to decide on a good allocation and scheduling scheme. There is no performance analysis of these heuristics and it is not clear how they would work for more general MDGs (DAGs). Our methods on the other hand have been theoretically analyzed for performance bounds and work well for general MDGs as we will show.

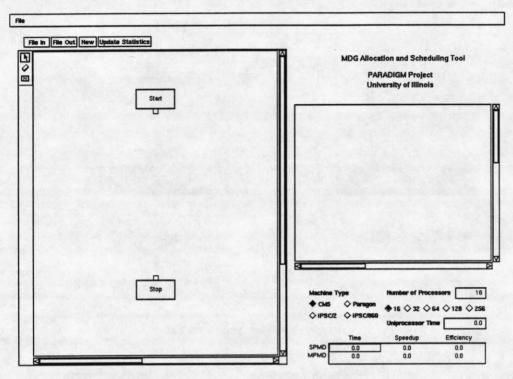

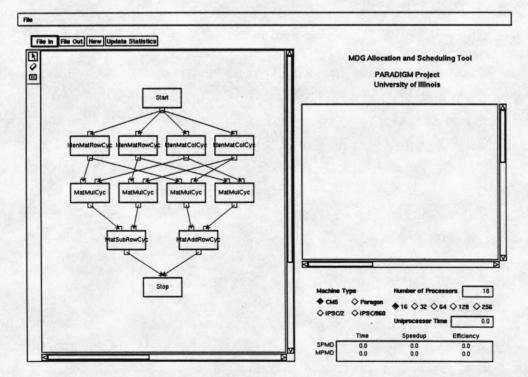

Figure 3: Startup View of MAST

### 1.4 MAST : MDG Allocation and Scheduling Tool

In order to provide an interface to our MDG allocation and scheduling methods, we designed and implemented MAST. Some of the ideas used for MAST are similar to the ones used for the HeNCE tool [32]. Basically, MAST provides users with the capability of specifying the MDG representation for their programs in a graphical manner. Once an MDG has been specified, MAST helps the user study the performance of his code on various architectures and run the code if needed on any of those architectures.

MAST has three major components to it:

- 1. A graphical programming tool

- 2. A library of parallel scientific routines whose execution is well profiled on all the desired target multicomputers

- 3. An allocation and scheduling tool based on the methods discussed in this paper

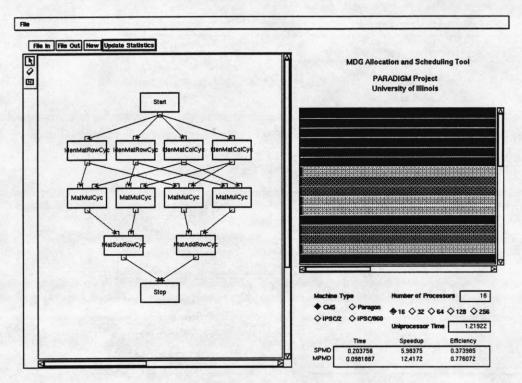

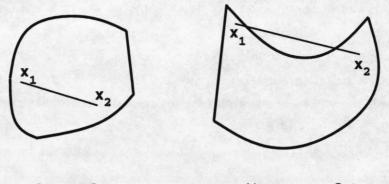

MAST ties up the three components and provides the user with various utilities. A step by step use of MAST has been shown in Figures 3 through 6. We now explain the significance of each figure:

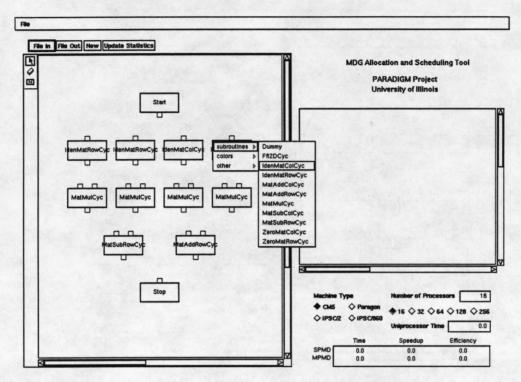

Figure 4: View of MAST After Nodes Have Been Drawn

Figure 5: View of MAST After a Complete MDG Has Been Drawn

Figure 6: View of MAST After an Update Statistics

- Figure 3 shows MAST when it is started up. At this point the graphical programming tool on the left half of MAST has only two nodes – START and STOP.

- Figure 4 shows MAST after the user has decided on the routines to be used in his program and placed the required nodes. Nodes are drawn using the one of the utilities of the graphical programming tool that can be seen on the top left corner of the canvas. Once a node has been drawn, it can be tied to a library routine using a pull down menu provided (shown in figure). On closer inspection of the figure, the nodes can be seen to have different routine names on them. It can also be seen that each node has little tag boxes on top and bottom; these represent the input and output arrays for the routine the node represents. Different routines have different numbers of tag boxes depending on their input and output array counts.

- Figure 5 shows MAST after the user has connected the nodes using the edge drawing utility of the graphical programming tool. Edges connect an output tag box of a node to an input tag box of another node. This indicates the array being written into by the first node is being read by the second node. Output tag boxes may have multiple edges, input tag boxes can have only one edge.

- Figure 6 shows MAST after the user has completed the MDG and has asked for a performance evaluation on a specified target architecture of a specified size. This performance evaluation uses the execution profile information of the scientific library. Performance statistics provided include predicted uniprocessor time, SPMD time and MPMD time. Speedup and efficiency predictions are also provided for the SPMD and MPMD cases; also provided is a Gantt chart showing the allocation and scheduling used for the MPMD case. In addition, MAST uses the allocation and schedule computed to generate source code containing:

- Calls to routines in the scientific library provided in MAST.

- Routines generated for data redistribution this is done using the work discussed in [22]. In that paper, techniques for redistributing arrays (for regular distributions) between arbitrary processor sets have been discussed.

- Routines generated to enable the scientific routines and redistribution routines to execute on subsets of processors. These routines are based on concepts similar to those of groups, contexts and communicators in MPI [33].

This generated code is ready to be compiled and executed on the target architecture.

In contrast to our graphical programming approach, other researchers in the area of integrating data and functional parallelism have used language extensions for specifying available data and functional parallelism. The work in [17, 29, 30] on the Fx compiler is based on extensions of FORTRAN which are used to specify functional and data parallelism. Data parallelism is specified using constructs similar to HPF and functional parallelism is specified using constructs called Parallel Sections. The FORTRAN-M language inherently provides constructs for specifying functional parallelism [18]; recent work proposes to integrate the language with HPF in order to specify data parallelism [34]. The work in [19] has proposed extensions to FORTRAN-90 for specifying functional parallelism.

In the next section, we provide a brief overview of the theory of convex and posynomial functions which we use in developing our allocation algorithm. In the following sections we discuss our allocation and scheduling algorithms. We then present our processing and data transfer cost models in Section 5. Theoretical results that discuss the optimality of our algorithms are provided in Section 6. Section 7 provides preliminary results obtained using our algorithms.

Convex Set

Non-convex Set

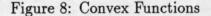

Figure 7: Convex sets.

## 2 Theory of Convex and Posynomial Functions

In this section we provide a brief overview of the theory of convex and posynomial functions. A detailed discussion of convex functions and convex programming can be found in Luenberger's book [35]. A discussion of the theory of posynomial functions is provided by Ecker in [36]. We have selected a few important and relevant points about these functions for our discussion here.

#### 2.1 Convex Sets

A set C in  $\mathbb{R}^n$  is said to be *convex* if, for every  $\mathbf{x}_1, \mathbf{x}_2 \in C$ , and every real number  $\alpha$ ,  $0 \leq \alpha \leq 1$ , the point  $\alpha \mathbf{x}_1 + (1 - \alpha) \mathbf{x}_2 \in C$ .

This definition can be interpreted geometrically as stating that a set is convex if, given two points in the set, every point on the line segment joining the two points is also a member of the set. Examples of convex and nonconvex sets are shown in Figure 7.

#### 2.2 Convex Functions

**Definition**: A function f defined on a convex set  $\Omega$  is said to be *convex* if, for every  $\mathbf{x}_1, \mathbf{x}_2 \in \Omega$ , and every  $\alpha, 0 \leq \alpha \leq 1$ ,

$$f(\alpha \mathbf{x}_1 + (1 - \alpha)\mathbf{x}_2) \le \alpha f(\mathbf{x}_1) + (1 - \alpha)f(\mathbf{x}_2).$$

(1)

f is said to be strictly convex if the inequality in Equation (1) is strict for  $0 < \alpha < 1$ .

Geometrically, a function is convex if the line joining two points on its graph is always above the graph. Examples of convex and nonconvex functions are shown in Fig 8.

**Convex Function**

Concave Function

Neither convex nor concave

#### 2.3 The Convex Programming Problem

The convex programming problem is stated as follows:

| $\begin{array}{ll} minimize & f(\mathbf{x})\\ such that & \mathbf{x} \in S \end{array}$ | (2)                |     |

|-----------------------------------------------------------------------------------------|--------------------|-----|

| such that                                                                               | $\mathbf{x} \in S$ | (3) |

where f is a convex function and S is a convex set.

This problem has the property that any local minimum of f over S is a global minimum, thereby easing the optimization process since it is unnecessary to perform hill-climbing out of local minima.

### 2.4 Posynomial Functions

A posynomial is a function g of a positive variable  $\mathbf{x} \in \mathbf{R}^n$  that has the form

$$g(\mathbf{x}) = \sum_{j} \gamma_{j} \prod_{i=1}^{n} x_{i}^{\alpha_{ij}}$$

(4)

where the exponents  $\alpha_{ij} \in \mathbf{R}$  and the coefficients  $\gamma_j > 0$ . A posynomial is a function that is similar to a polynomial, except that

- The coefficients  $\gamma_j$  must be positive.

- An exponent  $\alpha_{ij}$  could be any real number, and not necessarily a positive integer, unlike the case of polynomials.

A posynomial has the useful property that it can be mapped onto a convex function through an elementary variable transformation [36]

$$(x_i) = (e^{z_i}) \tag{5}$$

Such a functional form is very desirable, since such a transformation maps the problem of minimizing a posynomial function under posynomial constraints to a convex programming problem.

For example, the function  $3.7x_1^{1.4}x_2^{\sqrt{3}}+1.8x_1^{-1}x_3^{2.3}$  is a posynomial in the variables  $x_1, x_2, x_3$ . A few other examples include:

$$f(x_i) = 1/x_i \tag{6}$$

$$f(x_i) = constant \tag{7}$$

$$f(x_i, x_j) = \frac{x_i}{x_j} \tag{8}$$

$$f(x_i) = x_i \tag{9}$$

The fact that these functions are posynomials will be used later in the paper.

#### 2.5 A few Properties of Convex and Posynomial Functions

If f and g are convex functions defined on a convex set S, then the following properties hold:

Sum Property The functions f + g is a convex function over S.

Constant Property The function  $c \cdot f$ , where c is a non-negative constant, is a convex function over S.

Max Property The function  $\max(f,g)$  is a convex function over S.

Min Property The function  $\min(f, g)$  is a convex function over S.

As shown before, posynomials can be transformed to convex functions using Equation 5. Therefore, given two posynomial functions h and j defined on S, all the above properties hold for the pair. We will use these properties later in the paper.

## 3 MDG Allocation Algorithm

We first consider the problem of allocation of processors to the nodes of a given MDG. After the allocation is carried out using this algorithm, the MDG is ready to be scheduled using the algorithm described in the next section.

For the purposes of allocation and scheduling, we assume the given MDG has n nodes numbered consecutively from 1 to n. In addition, node 1 is the START node and node n is the STOP node.

To obtain an optimum solution to the allocation problem for a given MDG and a given p processor target system, we solve:

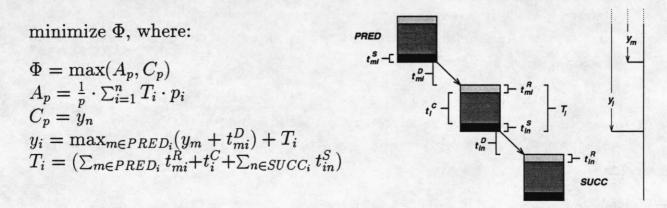

where

- 1.  $p_i$  represents the number of processors used by the *i*th node.

- 2.  $t_i^C$  is the processing cost of the routine corresponding to node *i* and is a function of  $p_i$ .

- 3.  $t_{mi}^{R}$  represents the time required at node *i* to process the messages it receives from predecessor node *m* (receiving cost component of data transfer).  $t_{mi}^{D}$  represents the network delay required between the completion of node *i* and the start of node *m* (network cost component of data transfer, weight of edge between nodes *m* and *i*).  $t_{in}^{R}$ represents the time required at node *i* to process messages it sends to successor node *n* (sending cost component of data transfer). All these quantities are functions of  $p_i$ and  $p_j$ .

- 4.  $PRED_i$  and  $SUCC_i$  are the sets of predecessor and successor nodes of node i in the given MDG, respectively.

- 5.  $T_i$  is the total time required to process node i (weight of node i).

- 6.  $y_i$  is the finish time of the *i*th node.

- 7.  $\Phi$  is the Optimum Finish Time obtainable for the execution of the program corresponding to the given MDG.

- 8.  $A_p$  is also called the Average Finish Time for the case when nodes use up to p processors each. To better understand the idea behind using the average finish time, consider a quantity called processor-time area for a node. This is the product of time taken for executing a node and the number of processors it uses. If we sum the processor-time areas for all nodes in the MDG, this will represent the minimum processor-time area requirement for the MDG. Another way of saying the same is that  $\Phi$  must be at least same as the average finish time which represents the sum of processor-time areas of all the nodes in the MDG averaged over p.

- 9.  $C_p$  is called the *Critical Path Time* for the case when nodes use up to p processors each. Since the critical path is the longest in the MDG, it represents the shortest possible time in which we can finish executing the MDG. This implies  $\Phi$  must be at least same as the critical path time.

The free variables in this formulation are the  $p_i$ 's, with  $1 \le p_i \le p$ , i = 1, n.

Our formulation relies on the properties of convex functions and posynomial functions discussed in the previous section. Basically, our allocation problem is equivalent to a convex programming formulation if the following conditions hold:

- 1.  $t_{ij}^D$ ,  $t_{ij}^R$ ,  $t_{ij}^S$ , and  $t_i^C$  can all be represented by posynomial functions of the free variables.

- 2.  $t_{ij}^R \cdot p_j, t_{ij}^S \cdot p_i$  and  $t_i^C \cdot p_i$  are also posynomial functions of the free variables.

Later, in Section 5, we present cost functions to represent the quantities  $t_{ij}^D$ ,  $t_{ij}^R$ ,  $t_{ij}^S$ , and  $t_i^C$  which satisfy these conditions. We also demonstrate the practicality of these functions.

The discussion above implies that in practice, we can construct a formulation equivalent to a convex programming formulation for allocation, and, therefore, obtain a unique minimum value for  $\Phi$ . The allocation that corresponds to this value will be an optimum allocation for the given MDG. This method of allocation inherently assumes the existence of a perfect scheduler, i.e. one that can produce a schedule which finishes the program in  $\Phi$  time units. In practice, producing such a schedule is an NP-Complete problem [26]. We therefore, use a scheduler as described in the next section which might produce a finish time different from  $\Phi$ . As we will show in Section 6, we have quantified this deviation.

## 4 MDG Scheduling Algorithm

To schedule a given MDG with processor allocation done according to the method described in the previous section, we use an algorithm called the *Prioritized Scheduling Algorithm* (PSA). The steps involved in the PSA are:

- 1. The processor allocation produced by the convex programming formulation will be a set of positive real numbers in the general case, however, we cannot allocate processors in this manner on a real system. In this step we round-off the allocated processors for all the nodes to the nearest power of 2. This is done to make the final code generation very easy. The results we obtain in Section 7 will show that this does not result in much loss in practice. We refer to this step in the sections that follow as the rounding-off step.

- 2. The rounded-off processor allocation for the MDG is then modified to impose a bound (PB) on the number of processors used by any node. If the *i*th node uses  $p_i$  processors and  $p_i > PB$ ,  $p_i$  is reduced to PB, else it is left unchanged. It can be seen that PB has to be a power of two or else we will have to round-off again and that may lead to a violation of the bound. The value of PB to be used is determined using Theorem 3 which is discussed in Section 6. We refer to this step in the sections that follow as the bounding step.

- 3. Since the processor allocation for the MDG may have been changed from the value produced by the allocation step, we need to re-compute the weights of the nodes and the edges of the MDG based on the new allocation. Next, we place the node START on a queue called the ready queue and mark its Earliest Start Time (EST) as 0.

- 4. In this step, we pick a node from the ready queue that has the lowest possible EST. We then check to see the time at which the processor requirement of this node can be met, i.e., the time at which the required processors will be done with the node(s) they are currently processing and can accept another node. This is called the Processor Satisfaction Time (PST). If  $PST \ge EST$ , the node can be scheduled at PST else, it can be scheduled only at EST. It must be noted that there will be some idle time in

the latter case since the required processors are available but not used. However, the scheduler is not forcing idleness, it simply does not have any other node to schedule since we have picked the node with the lowest EST.

- 5. If the node just scheduled is the STOP node, the scheduler is terminated else, we go to the next step.

- 6. After scheduling the node, we now check to see if any of its successors have all their predecessors scheduled, i.e. have their precedence constraints satisfied. If so, we compute the EST for those nodes based on the node and edge weights of the MDG and the schedule built so far. Such nodes are then placed in the ready queue.

- 7. Steps are repeated starting at Step 4.

The finish time of the STOP node based on the schedule is the predicted finish time of the program.

The scheduling algorithm described above is a variant of the popular List Scheduling Algorithm (LSA) which has been used for example, by Liu in [37], by Garey, Graham and Johnson in [38], by Wang and Cheng in [39], by Belkhale and Banerjee in [13], by Turek, Wolf and Yu in [40], and, by Ramaswamy and Banerjee in [14, 15]. It must be noted that some of the mentioned researchers also use variants of the LSA. We call it the PSA because of the implicit prioritization in Step 4 where a node with the lowest EST is picked even though other nodes may be ready for scheduling.

In the case where the number of processors used by any node is bounded, the PSA is shown to be within a factor of the optimum in Theorem 1 in Section 6. While similar results have been shown in the references mentioned above when there are no data transfer costs, our result is unique in that it takes into account these costs. In fact, it is the first such result to be derived.

## 5 Mathematical Cost Models

This section deals with the important aspect of choosing appropriate functions to represent the processing and data transfer costs involved in an MDG. The cost functions we choose have to satisfy two criteria; they have to be convex or posynomial functions, and, they have to be practical. In this section we show that our cost functions are posynomials, their suitability is shown in Section 7. The processing cost function we use is an often used model. On the other hand, the data transfer cost functions are our own. The derivation of these functions is described in detail in [41].

#### **Processing Cost Model**

For the processing cost model, we use Amdahl's law, i.e., the execution time of the routine corresponding to the *i*th node  $(t_i^C)$  as a function of the number of processors it uses  $(p_i)$  is given by:

$$t_i^C = (\alpha_i + \frac{1 - \alpha_i}{p_i}) \cdot \tau_i \tag{10}$$

where  $\tau_i$  is the execution time of the routine on a single processor and  $\alpha_i$  is the fraction of the routine that has to be executed serially. It can be seen that:

$$0 \le \alpha_i \le 1$$

$$0 \le \tau_i \tag{11}$$

The way we calculated *alpha* and *tau* for the various routines used in our benchmarks is by actually measuring execution times for these routines as a function of the number of processors they use and then using linear regression to fit the measured values to a function of the form we have chosen. In the future, we are considering the use of static techniques to predict these values. At this point, we only wish to demonstrate that processing costs can be modeled by a function of the form shown above. As our results will show, our form models processing costs fairly accurately in practice.

## **Lemma 1** $t_i^C$ is a posynomial function w.r.t. $p_i$ .

**Proof**: From Equation 10 we can see that  $t_i^C$  is made of two components; a constant component  $\alpha_i \cdot \tau_i$  and a variable component  $\frac{(1-\alpha_i)\cdot\tau_i}{p_i}$ . The first component is a posynomial since it is a non-negative constant (under Equation 11). The second component has a non-negative constant factor multiplying a posynomial  $\frac{1}{p_i}$ . Under the Constant Property discussed in Section 2, this component is also a posynomial. Since both components are posynomials, using the Sum Property of Section 2,  $t_i^C$  is a posynomial.  $\Box$

**Lemma 2**  $t_i^C \cdot p_i$  is a posynomial function w.r.t.  $p_i$ .

**Proof**: Using Equation 10, we can write down:

$$t_i^C \cdot p_i = \alpha_i \cdot \tau_i \cdot p_i + (1 - \alpha_i) \cdot \tau_i \tag{12}$$

We can see that this equation has two components; a variable component  $\alpha_i \cdot \tau_i \cdot p_i$  which has a non-negative constant factor  $\alpha_i \cdot \tau_i$  multiplying a posynomial  $p_i$ . By the Constant Property of Section 2, this component is a posynomial. The other component in the equation above is a non-negative constant which is also a posynomial. Hence, using the Sum Property of Section 2, we see that  $t_i^C \cdot p_i$  is a posynomial.  $\Box$

We would like to point out that  $\alpha$  and  $\tau$  for a routine could depend on the size of data input to the routine. This does not affect the statements made in either Lemma above.

#### Data Transfer Cost Model

Here we consider the cost of redistribution of an array of data elements between the execution of two nodes of the MDG involving  $p_i$  and  $p_j$  processors at the sending and receiving ends respectively. For modeling such a transfer, we assume that the array is distributed evenly across the  $p_i$  sending processors initially, and across the  $p_j$  receiving processors finally. In addition, we assume that the number and sizes of messages will be same for each sending processor and for each receiving processor. For example, every sending processor may send 3 messages of 1000 bytes and every receiver may receive 5 messages of 1500 bytes. These are both valid assumptions for the realm of regular computations which we are dealing with.

The regular distributions of an array along any of its dimensions (size along dimension is S) across a set of p processors are classified into the following cases:

- ALL : All elements of the array along the dimension are owned by the same processor (p = 1)

- BLOCK : Elements of the array are distributed evenly across all the processors with each processor owning a contiguous block of elements of size S/p.

- CYCLIC : Elements of the array are distributed evenly across all the processors in a round robin fashion with each processor owning every *p*th element, the *i*th processor starting at element *i*.

- BLOCKCYCLIC(X): Elements of the array are distributed evenly across all the processors in a round robin fashion with each processor owning every *p*th block of X elements, the *i*th processor starting at the *i*th block of X elements.

Details of regular distributions can be found in [2, 1]. For our discussion of data transfer costs, the distribution of an array can change from any of those listed above to any other along one or more of its dimensions.

In considering costs for any type of array transfer from node i to node j, we have already seen that there will be three basic components : a sending component  $t_{ij}^S$ , a network component  $t_{ij}^D$ , and, a receiving component  $t_{ij}^R$ . We have also seen that  $t_{ij}^S$  is accounted for in the weight of node i,  $t_{ij}^D$  is taken to be the weight of the edge joining node i and node j, and,  $t_{ij}^R$ is accounted for in the weight of node j. The reason for doing this is that  $t^S$  and  $t^R$  require processor involvement, whereas  $t^D$  does not.

We propose the following expressions for the three cost components:

$$t_{ij}^{S} = S_{ij}(p_i, p_j) \cdot t_{ss} + L \cdot \frac{1}{p_i} \cdot t_{ps}$$

$$t_{ij}^{D} = \frac{L}{p_i \cdot S_{ij}(p_i, p_j)} \cdot t_n$$

$$t_{ij}^{R} = R_{ij}(p_i, p_j) \cdot t_{sr} + L \cdot \frac{1}{p_j} \cdot t_{pr}$$

(13)

where,

- L is the length (in bytes) of the array being transferred

- $t_{ss}, t_{ps}$  are the startup and per byte cost for sending messages from a processor

- $t_n$  is the network cost per message byte

- $t_{sr}$ ,  $t_{pr}$  are the startup and per byte cost for receiving messages at a processor

- $S_{ij}$  is the number of messages sent from each sending processor

- $R_{ij}$  is the number of messages received at each receiving processor.

Intuitively, the sending component  $(t_{ij}^S)$  for each sending processor involves a startup cost for each of the  $S_{ij}$  messages sent and a processing cost for its share of the array  $(\frac{L}{p_i})$ . The same logic holds for the receiving component for receiving processors. The network component represents the minimum delay required for messages to be delivered to the receiving processors after they have been sent from the sending processors. If we assume a pipelined network with no congestion effects, this delay will depend on the length of the last message

| Distribution   | Block Factor    |  |  |

|----------------|-----------------|--|--|

| ALL            | L               |  |  |

| BLOCK          | $\frac{L}{p_i}$ |  |  |

| CYCLIC         | 1               |  |  |

| BLOCKCYCLIC(X) | X               |  |  |

Table 1: Block Factors for Various Regular Distributions

| Distribution                    | Skip Factor   |

|---------------------------------|---------------|

| ALL                             | L             |

| BLOCK                           | L             |

| CYCLIC                          | $p_i$         |

| $\operatorname{BLOCKCYCLIC}(X)$ | $X \cdot p_i$ |

Table 2: Skip Factors for Various Regular Distributions

sent. By our assumption of equal sized messages, we see that the size of each message will be  $\frac{L}{p_i \cdot S_{ij}(p_i, p_j)}$ . This is the reasoning behind the network cost component expression shown.